SuVolta╝ęĪó╔┘╗╬─╠ż╦¶öżŁĪóARMĪóUMCż╚żŌĘ└╠¾Īó└«─╣┤ļČ╚żžŲ¦ż▀Įąż╣

MOSź╚źķź¾źĖź╣ź┐ż╬ź▓Ī╝ź╚żĘżŁżż┼┼░ĄVthż╬źąźķż─żŁż“╦▄ä®┼¬ż╦žōżķż╣Č\Įč┤ļČ╚ż╬SuVoltaĪ╩ź╣ź▄źļź┐Ī╦╝ęĪŻż│ż╬ż█ż╔ĪóARMź│źóżŪ╣Ō└Łē”Ī”─ŃŠ├õJ┼┼╬üż“╝┬Š┌Ī󿥿ķż╦UMCż╚28nmźūźĒź╗ź╣ż“Č”Ų▒│½╚»ż╣żļż│ż╚ż“╚»╔ĮżĘż┐ĪŻż│ż╬Č\Į迎ĪóVthźąźķż─żŁż“Š«żĄż»żŪżŁżļż┐żßĪó┼┼Ė╗┼┼░Ąż“▓╝ż▓ĪóŠ├õJ┼┼╬üż“║’žōżŪżŁżļĪŻ

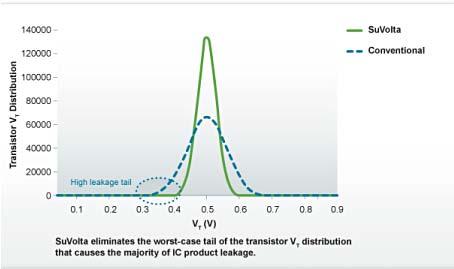

┐▐1ĪĪVthż╬źąźķż─żŁż¼Š«żĄżżż╚┼┼Ė╗┼┼░Ąż“▓╝ż▓żķżņżļĪĪĮąųZĪ¦SuVolta

“£═Ķż╬MOSź╚źķź¾źĖź╣ź┐Č\ĮčżŪżŽĪó╚∙║┘▓Įż╣żļż█ż╔Vthż¼źąźķż─ż»ż┐żßĪóżĮż╬ź▐Ī╝źĖź¾ż“╣═ż©żļż╚┼┼Ė╗┼┼░Ąż“▓╝ż▓żķżņż╩ż½ż├ż┐ĪŻĖĒŲ░║Ņż╣żļČ▓żņż¼ĮjżŁż»ż╩żļż┐żßż└ĪŻVthż╬źąźķż─żŁ╩¼╔█ż¼Š«żĄż▒żņżąź▐Ī╝źĖź¾ż“Ø▓╩¼ż╦ŲDżņżļż┐żßĪó┼┼Ė╗┼┼░Ąż“▓╝ż▓żŲżŌĖĒŲ░║ŅżĘż╩żżĪŻSuVoltaż╬Č\Į迎ż│ż╬Vthźąźķż─żŁż¼╦▄ä®┼¬ż╦Š«żĄżż(┐▐1)ĪŻżĘż½żŌż│ż╬Č\Į迎Īó┘J┘Tż╬Ö┌ŠÅ└▀×óż“ŠW├ōżĘżŲ×æļ]żŪżŁżļż╚żżż”ØŖ─╣żŌżóżļĪŻ┼Ļ½@╔ķ├┤ż¼ż½ż½żķż║ĪóŠ├õJ┼┼╬üż“▓╝ż▓Īó└Łē”ż“æųż▓żķżņżļĪŻ

Ų▒╝꿎2012ŃQ12ĘŅż╦╔┘╗╬─╠ź╗ź▀ź│ź¾ź└ź»ź┐Ī╝ż╦źķźżź╗ź¾ź╣ż“ČĪ═┐żĘĪó65nmźūźĒź╗ź╣Č\ĮčżŪ─ŃŠ├õJ┼┼╬üĪ”╣ŌÅ]ż╬Ė·▓╠ż“│╬Ū¦żĘżŲżżż┐ĪŻ║ŻövżŽĪóARMż╬Cortex-M0źūźĒź╗ź├źĄź│źóż╦SuVoltaż╬Č\Įčż“┼¼├ōżĘĪóŠ├õJ┼┼╬üż╬║’žōż╚Ų░║Ņ└Łē”ż╬Ė■æųż“│╬Ū¦żĘż┐żŌż╬ĪŻLSIż╬└Łē”┼¬ż╦żŽĪó1└ż┬ÕęÆżņż┐źūźĒź╗ź╣żŪżŌĪó┐╩ż¾ż└źūźĒź╗ź╣ż╚Ų▒żĖØŖ└Łż“Įąż╗żļĪŻ

É║öü┼¬ż╦żŽĪóARM Cortex-M0źūźĒź╗ź├źĄź│źóż““£═ĶźūźĒź╗ź╣ż╚SuVoltaż╬DDCĪ╩Deeply Depleted ChannelĪ¦┐╝żżČ§Ēś┴žż╬ź┴źŃź¾ź═źļż“ŠW├ōż╣żļź╚źķź¾źĖź╣ź┐Č\ĮčĪ╦źūźĒź╗ź╣żŪżĮżņżŠżņ×æ║ŅżĘĪóØŖ└Łż“╚µ│ėżĘż┐ĪŻżĮż╬±T▓╠Ī󟻟Ēź├ź»╝■āS┐¶ż“ż╔ż┴żķżŌ350MHzżŪŲ░║ŅżĄż╗żļż╚ĪóDDCČ\ĮčżŪ║Ņż├ż┐M0źūźĒź╗ź├źĄżŽŠ├õJ┼┼╬üż¼50%▓╝ż¼ż├ż┐ĪŻż▐ż┐Š├õJ┼┼╬üż¼Ų▒żĖż╦ż╩żļżĶż”ż╦ź»źĒź├ź»╝■āS┐¶ż“╩čż©żļż╚┐ĘČ\Įčż╦żĶżļźūźĒź╗ź├źĄż╬Ų░║ŅÅ]┼┘żŽ35%Ė■æųĪó┼┼Ė╗┼┼░Ąż“Ų▒▐kż╦żĘżŲŲ░║ŅżĄż╗żļż╚Å]┼┘żŽ55%Ė■æųżĘż┐ż╚żĘżŲżżżļĪŻ

DDCź╚źķź¾źĖź╣ź┐żŪSRAMż“║Ņż├ż┐ż¼ĪóSRAMżŽ150mVż╚żżż”─Ń┼┼░ĄżŪŲ░║ŅżĘż┐ż╚żżż”ĪŻżĄżķż╦ĪóŲ╔ż▀ĮążĘŲ░║ŅżŪż╬źĻĪ╝ź»┼┼╬«ż╦żĶżļ┼┼╬üżŽ50%▓╝ż¼żĻĪóźŪĪ╝ź┐ż“╩▌Ęeż╣żļźĻźŲź¾źĘźńź¾źŌĪ╝ź╔żŪż╬źĻĪ╝ź»┼┼╬üżŽ1/5░╩▓╝ż╦ż╩ż├ż┐ż╚żĘżŲżżżļĪŻ

SuVoltażŽżĄżķż╦UMCż╚28nmźūźĒź╗ź╣ż“Č”Ų▒│½╚»ż╣żļż│ż╚ż“╚»╔ĮżĘż┐ĪŻ28nmźūźĒź╗ź╣żŪ└ĶŲ¼ż“╣įż»TSMCż¼║“ŃQĪóÖ┌ŠÅ╩Ōé╬ż▐żĻż¼æųż¼żķż╩ż»żŲ28nm LPźūźĒź╗ź╣ż“ŠW├ōżĘż┐źóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄż╬Ö┌ŠÅż¼┤ųż╦╣ńż’ż╩ż½ż├ż┐ĪŻTSMCż╬ĖÕ┐ąż“ŪężĘżŲżżżļUMCż¼28nmźūźĒź╗ź╣ż“▓├Å]żĘżŲTSMCż╦╝{żż¤²żŁ/╝{żż▒█ż╣ż┐żßż╦żŽĪó“£═Ķż╬ź╚źķź¾źĖź╣ź┐żŪżŽÖ┌ŠÅ╬®ż┴æųż▓ż¼ęÆżņżŲżĘż▐ż”Č▓żņż¼żóżļĪŻVthż╬źąźķż─żŁż¼Š»ż╩ż▒żņżą╩Ōé╬ż▐żĻĖ■æųżõÖ┌ŠÅ╬®ż┴æųż▓ż“┴ßż»żŪżŁżļżŽż║ĪŻ

UMCż¼ĖĮ║▀│½╚»├µżóżļżżżŽĮą▓┘├µż╬28nmźūźĒź╗ź╣ż╬LSIż╦┤žżĘżŲżŌĪóźĻĪ╝ź»┼┼╬«ż╬¾Hżżź╚źķź¾źĖź╣ź┐ż└ż▒ż“DDCź╚źķź¾źĖź╣ź┐ż╦ÅøżŁ┤╣ż©żļż╚żżż”ź¬źūźĘźńź¾ż╚Īóż│żņż½żķ│½╚»ż╣żļżĶż”ż╩LSIżŪżŽµ£żŲż╬ź╚źķź¾źĖź╣ź┐ż“DDCź╚źķź¾źĖź╣ź┐żŪ└▀╝Ŗż╣żļĪóż╚żżż”ź¬źūźĘźńź¾żŪ╬Š╝꿎╣ń┴TżĘżŲżżżļĪŻUMCż╬└Ķ├╝Č\Įčŗ╠ńźąźżź╣źūźņźĖźŪź¾ź╚ż╬T. R. YewĢ■żŽĪóĪųSuVoltaż╬└Ķ├╝Č\Įčż“┼÷╝ęż╬HKMGĪ╩źŽźżK/źßź┐źļź▓Ī╝ź╚Ī╦źūźĒź╗ź╣ż╦Ų│Ų■ż╣żļż│ż╚ż╦żĶż├żŲĪó┘J┘Tż╬ź▌źĻSiONźūźĒź╗ź╣ż╚┴Ļ▌öż├żŲĪó28nmźŌźąźżźļź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż╬ż┐żßż╬źūźĒź╗ź╣źūźķź├ź╚źšź®Ī╝źÓż“─¾ČĪżĘżŲżżżŁż┐żżż╚╗ūż├żŲżżż▐ż╣Īūż╚Ėņż├żŲżżżļĪŻ

┐▐2ĪĪSuVoltaż╬COOż╦┼×ŪżżĘż┐Louis ParrilloĢ■

SuVoltażŽĪóDDCČ\Įčż“źķźżź╗ź¾ź╣ČĪ═┐ż╣żļIPź┘ź¾ź└Ī╝żŪżóżĻĪóČ\Įč╬üż“ź”źĻż╦ż╣żļŲ¼╦N┤ļČ╚ż└ĪŻż½ż─żŲBell LaboratoriesżŪCMOSź─źżź¾ź┐źųČ\Įčż“│½╚»żĘĪóMotorolaĪóRambusżŪĘą▒─ŗ╠ńż“Ęą┘xżĘżŲżŁż┐Louis ParrilloĢ■ż“23Ų³ż╦COOĪ╩║Ū╣Ō╝╣╣į└šŪżŪvĪ╦ż╦Ūż╠┐żĘż┐ż╚╚»╔ĮżĘż┐ĪŻŲ▒Ģ■żŽ×æļ]źčĪ╝ź╚ź╩Ī╝╝ę┐¶ż“ż╣żŪż╦6╝ę░╩æųżŌ╗\żõżĘż┐ż╚żżż”ĪŻSuVolta╝ęż╦żŽĪóĮjŠ}Ń~ć@ż╩ź┘ź¾ź┴źŃĪ╝źŁźŃźįź┐źļ(VC)żŪżóżļź»źķźżź╩Ī╝Ī”źčĪ╝źŁź¾ź╣Ī”ź│Ī╝źšźŻĪ╝źļź╔Ī§źąźżźõĪ╝ź║żõź¬Ī╝ź¼ź╣ź╚źŁźŃźįź┐źļż╩ż╔ĪóżĮż”żĮż”ż┐żļż╚ż│żĒż¼Įą½@żĘżŲżżżļĪŻ