IBMĖ”ē|ĮĻż¼2nmźūźĒź╗ź╣żŪ500▓»ź╚źķź¾źĖź╣ź┐ż╬ICź┴ź├źūż“╗Ņ║Ņ

ä▌ź╦źÕĪ╝źĶĪ╝ź»ä”źóźļźąź╦Ī╝ż╦ż¬ż▒żļIBMĖ”ē|ĮĻż¼2nmźŪźČźżź¾ż╬ź╩ź╬źĘĪ╝ź╚Č\Įčż“╗╚ż├ż┐ź╚źķź¾źĖź╣ź┐ż“│½╚»Īóż│ż╬ź╚źķź¾źĖź╣ź┐ż“500▓»Ė─ĮĖ└čżĘż┐ICźŲź╣ź╚ź┴ź├źūż“300mmź”ź¦Ī╝źŽæųż╦╗Ņ║ŅżĘż┐Ī╩┐▐1Ī╦ĪŻIBMżŽĪóPowerźóĪ╝źŁźŲź»ź┴źŃż╬CPUż“Ų╚śOż╦│½╚»żĘżŲżżżļż¼Īó║ŻŃQĖÕ╚Šż╦7nmźūźĒź╗ź╣ż╬Power10ż“źĻźĻĪ╝ź╣ż╣żļż┐żßĪó2nmź┴ź├źūż¼┼ąŠņż╣żļż╬żŽ2025ŃQ░╩æTż╦ż╩żĻżĮż”ż╚Ė½żķżņżŲżżżļĪŻ

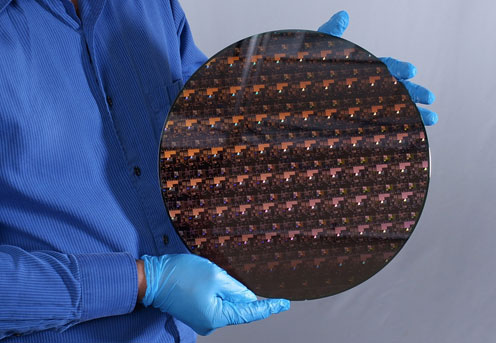

┐▐1ĪĪIBMż╬2nmź╚źķź¾źĖź╣ź┐ĪĪĮąųZĪ¦IBM Corp.

IBMżŽż│żņż▐żŪ2015ŃQż╦7nmż╬źŲź╣ź╚ź┴ź├źūĪó2017ŃQż╦5nmż╬źŲź╣ź╚ź┴ź├źūż“żĮżņżŠżņ│½╚»żĘżŲż¬żĻĪó║Żövż╬2nmź┴ź├źūżŽżĮż╬╝Īż╦┼÷ż┐żļĪŻ

║ŻövČ╚─cĮķż╬2nmźŪźČźżź¾ICżŽĪóĖĮ║▀ż╬7nmź┴ź├źūż╚╚µż┘Īó└Łē”ż¼45%╣Ōż»ĪóŠ├õJ┼┼╬üżŽ75%─Ńżżż╚Ė½└čżŌż├żŲżżżļĪŻIBMż╬źūźņź╣źĻźĻĪ╝ź╣ż╦ĘŪ║▄żĄżņżŲżżżļĪųĖ½└čżŌż├żŲżżżļĪūż╚żżż”╔ĮĖĮżŽĪóż▐ż└╝┬▒R├═żŪżŽż╩żĄżĮż”ż└ĪŻ

2nmż▐żŪ╚∙║┘ż╦ż╣żļż╚ĪóĘ╚┬ė┼┼ÅBż╬źąź├źŲźĻÖæ╠┐żŽ4Ū▄ż╦─╣ż»ż╩żĻĪó├ŽĄÕµ£öüż╬ź©ź═źļź«Ī╝ż╬1%ż“Š├õJżĘżŲżżżļźŪĪ╝ź┐ź╗ź¾ź┐Ī╝żŪżŽCO2ŪėĮąż¼Ś„žōż╣żļż╚żĘżŲżżżļĪŻżĄżķż╦Īóź╬Ī╝ź╚PCżŽ╦▌Ślż¼į~├▒ż╦żŪżŁżļżĶż”ż╦ż╩żĻĪóźųźķź”źĖź¾ź░ż╬Å]┼┘żŌÅ]ż»ż╩żļż╚żżż”ĪŻśOŲ░▒┐┼Š┘Zż╬żĶż”ż╩śO淟ʟ╣źŲźÓż╬▒■┼·żŌ╣ŌÅ]ż╦ż╩żļż╚żĘżŲżżżļĪŻ

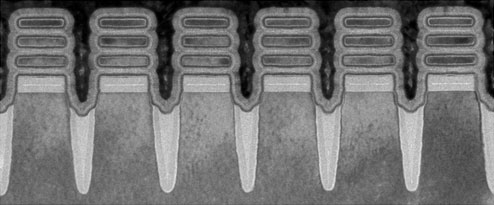

ż│ż╬ź╚źķź¾źĖź╣ź┐żŽGAAĪ╩Gate All AroundĪ╦╣Įļ]ż╦Ė½ż©żļż¼Ī╩┐▐2Ī╦Īóź╚źķź¾źĖź╣ź┐ŗ╩¼ż╦ź╩ź╬źĘĪ╝ź╚Č\Įčż“╗╚ż├żŲżżżļĪóż╚ĄŁŪv▓±Ė½ż╦Įą└╩żĘż┐Semiconductor DigestįćĮĖ─╣ż╬Pete SingerĢ■żŽĮęż┘żŲżżżļĪ╩╗▓╣═½@╬┴1Ī╦ĪŻ┐▐2ż╦żŽ6Ė─ż╬ź╚źķź¾źĖź╣ź┐ż╬éāĀCż“┐āżĘżŲż¬żĻĪóź╚źķź¾źĖź╣ź┐1Ė─ż╦3ĮŚż╬ź╩ź╬źĘĪ╝ź╚ż“┤▐ż¾żŪż¬żĻĪóĘQź╩ź╬źĘĪ╝ź╚ż╬╔²żŽ14nmĪó╣ŌżĄżŽ5nmż└ż╚żżż”ĪŻź╚źķź¾źĖź╣ź┐ż╬ź▓Ī╝ź╚─╣żŽ12nmżŪĪóź╚źķź¾źĖź╣ź┐┤ųż╬╩¼▀`ż╦żŽźąźļź»ż╬═Č┼┼öü╩¼▀`ż“╗╚ż├żŲżżżļĪŻEUVźĻźĮź░źķźšźŻżŪź╩ź╬źĘĪ╝ź╚ż╬╔²ż“15~70nmż╦▓├╣®ż╣żļż│ż╚ż¼żŪżŁżļż╚żżż”ĪŻĘQź╚źķź¾źĖź╣ź┐ż╬źįź├ź┴żŽ44nmĪŻ

┐▐2ĪĪź╩ź╬źĘĪ╝ź╚ź╚źķź¾źĖź╣ź┐éāĀCĪĪ6ź╚źķź¾źĖź╣ź┐ż“┐āż╣ĪĪĮąųZĪ¦IBM Corp.

IBMżŽ7nmźūźĒź╗ź╣ż╬╗■ż½żķEVUż“╗╚ż├żŲżŁż┐ż¼ĪóŪ█└■╣®µćżõ¾H┴žŪ█└■╣®µćż╦┼¼├ōżĄżņżŲżŁż┐ĪŻ║ŻövżŽĮķżßżŲź╚źķź¾źĖź╣ź┐╣®µćżŪEUVż“╗╚ż├ż┐ż╚żĘżŲżżżļĪŻ║Żövż╬╗Ņ║ŅżŪżŽĪóź╣ź┐ź├ź»ź╚CMOS╣Į└«ż“ŲDżķż╩ż½ż├ż┐ż¼ĪóĮø═ĶżŽżóżĻż”żļż╚żĘżŲżżżļĪŻ

Įø═Ķż╬╬╠ŠÅ╣®µćżŪżŽĪóIBMżŽIntelż¬żĶżėSamsungż╚żŽČ╚ē»─¾Ę╚ż“±Tż¾żŪż¬żĻĪó╚Óżķż╚ź©ź│źĘź╣źŲźÓż“Ę┴└«żĘżŲżżżļż┐żßĪó2nmź┴ź├źūż╬×æļ]żŽż¬żĮżķż»Samsungż╦ż╩żļż└żĒż”ĪŻ

╗▓╣═½@╬┴

1. IBM Unveils WorldĪŪs First 2 nm Chip Technology (2021/05/06)