Micronż╬232┴žNANDźšźķź├źĘźÕżŽ1Tźėź├ź╚ż╬╣ŌĮĖ└č+2.4GB/sż╬╣ŌÅ]▓Į

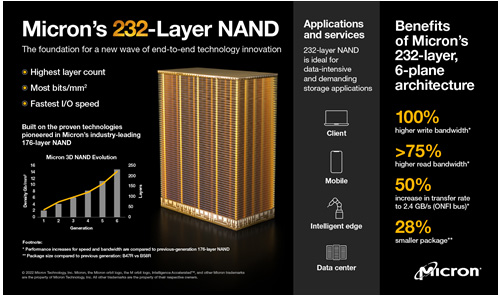

Micron Technologyż¼ż│żņż▐żŪ║Ū¾Hż╬ź╗źļ┴ž┐¶żŪżóżļ232┴žż╬3D-NANDźšźķź├źĘźÕźßźŌźĻż“│½╚»Ī╩┐▐1Ī╦ĪóżĮżņż“┼ļ║▄żĘż┐Crucialźųźķź¾ź╔ż╬SSDż╬źĄź¾źūźļĮą▓┘ż“Ė┬─ĻźµĪ╝źČĪ╝Ė■ż▒ż╦╗Žżßż┐Ī╩╗▓╣═½@╬┴1Ī╦ĪŻ╬╠ŠÅżŽ2022ŃQ¼Źż╦ż╩żļĖ½╣■ż▀ż└ĪŻ232┴žż╚3źėź├ź╚/ź╗źļČ\ĮčżŪNANDźšźķź├źĘźÕżŽ1Tźėź├ź╚ż╬ź┴ź├źūż╚2Tźąźżź╚ż╬źčź├ź▒Ī╝źĖ═Ų╬╠ż“╝┬ĖĮżŪżŁżļż╚żżż”ĪŻ

┐▐1ĪĪMicronż╬│½╚»żĘż┐232┴ž3D-NANDżŽ╣ŌÅ]▓ĮżŌ├Ż└«ĪĪĮąųZĪ¦ Micron Technology

ż│żņż▐żŪMicronżŽĪó176┴žż╬NANDźšźķź├źĘźÕż“╚»╔ĮżĘżŲż¬żĻĪ╩╗▓╣═½@╬┴2Īó3Ī╦ĪóżĮż╬╗■żŽ88┴žż╬NANDźšźķź├źĘźÕ┴žż“2├╩└čżÓż│ż╚żŪ176┴žż“╝┬ĖĮżĘżŲżżż┐ĪŻ┼÷╗■żŽ88┴žż“×æļ]ż╣żļż╬ż╦ØŁ═ūż╩┐╝ż»żŲźąźķż─żŁż╬Š»ż╩żżź©ź├ź┴ź¾ź░ż╬╗@┼┘żŽĪó88┴žż¼Ė┬─cż└ż╚Ėņż├żŲżżż┐ż¼ĪóżĮż╬Ė┬─cż“Ų═Ū╦żĘż┐ż╚żżż©żĮż”ż└ĪŻ

║ŻövżŽźūźĒź╗ź╣ż╦ż¬ż▒żļ┴ž┐¶ż“116┴žż╚żĘż┐ż│ż╚żŪĪóżĮżņżķż“2ĮŚ─_ż═żŲ232┴žż“╝┬ĖĮżĘż┐ĪŻż│żņż▐żŪSamsungżŽ100┴žµć┼┘ż¼×æļ]ż╬Ė┬─cż╚Įęż┘żŲż¬żĻĪóż│ż╬Ė┬─cżŌŲ═Ū╦żĘż┐ż│ż╚ż╦ż╩żļĪŻ┴ž┐¶ż“╣Ōżßż┐ż│ż╚żŪĪóĮĖ└č╠®┼┘żŽ14.6Gźėź├ź╚/mm2ż╚ż╩żĻĪóŲ▒żĖ3źėź├ź╚/ź╗źļĪ╩TLCĪ╦ż╬Ēö╣ń×æēäż╬35~100%ż╬ĀC└čż╦ż╩żļż╚żĘżŲżżżļĪŻ

ż▐ż┐Ų╔ż▀ĮążĘż╬I/OÅ]┼┘żŽĪó2.4Gźąźżź╚/╔├ż╚Å]żżĪŻż│żņżŽźßźŌźĻź╗źļźóźņźżż““£═Ķ4╩¼│õĪ╩4źūźņĪ╝ź¾Ī╦żĘżŲżżż┐ż╬ż╦×┤żĘżŲĪó6╩¼│õĪ╩6źūźņĪ╝ź¾Ī╦ż╦ż╣żļż│ż╚żŪ╣ŌÅ]▓ĮżĘż┐ĪŻ▐k╚╠ż╦ĪóźßźŌźĻ═Ų╬╠ż“æųż▓żļż╬ż╦“£żżĪóź╗źļż▐żŪż╬š{▀`ż¼─╣ż»ż╩żĻźóź»ź╗ź╣ż¼ęÆż»ż╩ż├żŲżĘż▐ż”Č▓żņż¼żóżļĪŻż│ż╬ż┐żßĪóź╗źļźóźņźżż“╩Ż┐¶ż╦╩¼│õż╣żļż│ż╚żŪĪóź╗źļż╦źóź»ź╗ź╣ż╣żļż▐żŪż╬š{▀`ż“ø]ż»żĘ╣ŌÅ]ż╦Ų╔ż▀Įąż╣╣®╔ūż“żĘżŲżżżļĪŻŲ╔ż▀ĮążĘÅ]┼┘ż“æųż▓żļż│ż╚ż╦żĶż├żŲĪó─ŃźņźżźŲź¾źĘżŪ╣Ōź╣źļĪ╝źūź├ź╚ż╬źŪĪ╝ź┐ź╗ź¾ź┐Ī╝╗┼══żõAIĪóØÖ╣Įļ]▓ĮźŪĪ╝ź┐ź┘Ī╝ź╣Ī󟻟ķź”ź╔ź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż╩ż╔ż╦Ė■ż»ż╚żĘżŲżżżļĪŻ

Micronż╬╣ŌĮĖ└č3D-NANDźšźķź├źĘźÕżŪżŽĪóCMOSź╚źķź¾źĖź╣ź┐╣Įļ]ż╬æųż╦źßźŌźĻźóźņźżż“Ę┴└«ż╣żļCMOS under ArrayĪ╩CuAĪ╦ż“║╬├ōżĘżŲżżżļĪŻ┴ž┐¶ż“232┴žż╦╗\żõżĘż┐ż│ż╚żŪĪó║ŪĮj1Tźėź├ź╚ż╬ź┴ź├źūż“Ę┴└«żŪżŁżļż╚żżż”ĪŻ176┴žż╬Øi└ż┬Õż╚╚µż┘źčź├ź▒Ī╝źĖźĄźżź║ż“28%Š«żĄż»żĘĪó11.5mmĪ▀13.5mmż╬źčź├ź▒Ī╝źĖż╦╝²═ŲżŪżŁżļż╚żĘżŲżżżļĪ╩╗▓╣═½@╬┴4Ī╦ĪŻż│żņż╦żĶżĻØi└ż┬ÕżĶżĻ50%╣ŌÅ]ż╬2400MT/╔├ż╬ONFIĪ╩Open NAND Flash InterfaceĪ╦┼Š┴„Å]┼┘ż“įużŲżżżļĪŻ

╗▓╣═½@╬┴

1. Īųź▐źżź»źĒź¾Īó└ż─cĮķż╬232┴žNANDż“Įą▓┘│½╗ŽżĘĪóźŲź»ź╬źĒźĖĪ╝Ī”źĻĪ╝ź└Ī╝źĘź├źūż“│╚ĮjĪūĪóMicron (2022/07/27)

2. ĪųMicronĪó176┴žż╚żżż”║Ū╣Ō┴žż╬NANDźšźķź├źĘźÕż“źĄź¾źūźļĮą▓┘ĪūĪóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ (2020/11/10)

3. ĪųMicronż¼176┴žNANDźšźķź├źĘźÕż╬└▀╝Ŗ╗ū„[ż“£½żķż½ż╦ĪūĪóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ(2020/11/19)

4. "First to Market, Second to None: the WorldĪŪs First 232-Layer NAND", Micron (2022/07/26)