TSMCż¼N2źūźĒź╗ź╣ż▐żŪż╬└’ŠSż“╚»╔ĮĪó│½╚»┼Ļ½@żŽż▐ż╣ż▐ż╣Ą±Yż╦

TSMCż¼8ĘŅ30Ų³ż╦±śŽčżŪTechnology Symposiumż“│½╠¢żĘż┐ĖÕĪó║ŻövżŽ3ŃQżųżĻż╦Ų³╦▄ż╦╬®ż┴┤¾żĻżĮż╬▄ćŠSż“Šę▓ĪóN2źūźĒź╗ź╣ź╬Ī╝ź╔ż▐żŪż╬źĒĪ╝ź╔ź▐ź├źūż“┐āżĘż┐ĪŻż┐ż└Īó1╝ĪĖĄ┼¬ż╩╚∙║┘▓ĮØó╦ĪżŽżŌżŽżõ┴T╠Żż¼ż╩ż»ĪóTSMCżŽ1╝ĪĖĄ┼¬ż╩ź╣ź▒Ī╝źĻź¾ź░ż½żķ2╝ĪĖĄ┼¬ż╩ĀC└čź╣ź▒Ī╝źĻź¾ź░żžż╚źĘźšź╚żĘżŲżŁżŲżżżļĪŻŲ▒╝ęźėźĖź═ź╣│½╚»ż╬źĘź╦źóVPĪóKevin ZhangĢ■Ī╩┐▐1Ī╦ż╦Ų▒╝ęż╬└’ŠSż“╩╣ż»ĪŻż╩ż¬Īó9ĘŅ28Ų³ż╦│½╠¢═Į─Ļż╬ź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ▓±µ^Ė┬─ĻFree WebinarżŽĪųTSMCĖ”ē|Īūż¼źŲĪ╝ź▐żŪżóżļĪŻ

┐▐1ĪĪTSMCźėźĖź═ź╣│½╚»├┤┼÷SVPż╬Kevin ZhangĢ■

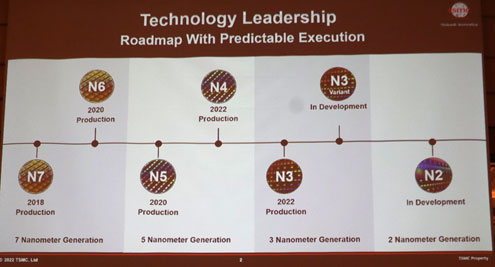

╚∙║┘▓Įź┴ź├źūż╬╝┬Øó╦Īż¼15nmØiĖÕżŪ┘Vż▐ż├żŲżżżļż│ż╚żŽ║ŪŖZżĶż»ē¶żķżņżļżĶż”ż╦ż╩ż├ż┐ĪŻ╬Ńż©żąTSMCż╬7nmźūźĒź╗ź╣żŽIntelż╬10nmźūźĒź╗ź╣ż╦ŖZżżż╚żżż’żņżŲż¬żĻĪóźßź┐źļźįź├ź┴żŽżżż║żņżŌ40┐¶nmżŪżóżļĪŻØŖż╦16nmźūźĒź╗ź╣ż╚Š╬żĘżŲżżż┐FinFETź╚źķź¾źĖź╣ź┐ż“Ų│Ų■żĘżŲż½żķż╬źūźĒź╗ź╣Č\Įčż¼źūźĒź╗ź╣ź╬Ī╝ź╔ż╬┐¶ÖCż╚Īó╝┬Øó╦Īż╚ż╬ą¬▀`ż¼Ś„żĘż»ż╩ż├żŲżżżļĪŻżŌżŽżõØó╦Īż╬╚∙║┘▓ĮĪ╩Ū█└■╔²Ī”Ū█└■┤ų│ųĪ╦żŽż█ż▄┘Vż▐ż├żŲż¬żĻĪó1╝ĪĖĄ┼¬ż╩╚∙║┘▓Įź╣ź▒Ī╝źĻź¾ź░żŽĪó2╝ĪĖĄ┼¬ż╩ź©źĻźóĪ╩ĀC└čĪ╦ź╣ź▒Ī╝źĻź¾ź░żžż╚╩čż’ż├ż┐ĪŻ

Ų▒╝ęźėźĖź═ź╣│½╚»ż╬źĘź╦źóVPĪóKevin ZhangĢ■Ī╩┐▐1Ī╦żŽĪóżĮżņżŪżŌ╚∙║┘▓ĮØó╦Īż“╗╚ż├żŲźūźĒź╗ź╣ż╬┐╩·tż“╔Į┐āżĘżŲżżżļĪŻż┐ż└Ī󿥿╣ż¼ż╦IntelżŽnmźūźĒź╗ź╣ż╚żŽĖ└ż’ż║Īó7nmźūźĒź╗ź╣┴Ļ┼÷ż╬PPAĪ╩PerformanceĪóPowerĪóAreaĪ╦żŪżóżņżąIntel 7ż╚Ō}żėĪóTSMCżŽN7ż╚Ō}żųżĶż”ż╦ż╩ż├ż┐Ī╩┐▐2Ī╦ĪŻż┐ż└żĘĪóĖ²Ų¼żŪżŽ┴Ļ╩čż’żķż║7nmĪ╩ź╩ź╬źßĪ╝ź╚źļĪ╦ż╚żżż”Ė└±äż“╗╚ż├żŲżżżļĪŻ

┐▐2ĪĪTSMCż¼ķWż»╚∙║┘▓Įż╬Č\ĮčźĒĪ╝ź╔ź▐ź├źūĪĪ

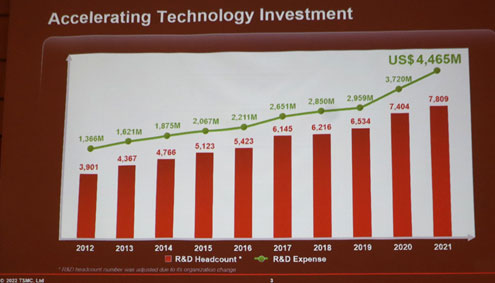

Appleż╬ź╣ź▐Ī╝ź╚źšź®ź¾iPhone 13ż╦╗╚ż’żņżŲżżżļA14źŌźąźżźļźūźĒź╗ź├źĄżŽN5źūźĒź╗ź╣żŪÖ┌ŠÅżĄżņżŲżżżļż¼Īó2020ŃQż╦Ö┌ŠÅ│½╗ŽżĘż┐N5żóż┐żĻż½żķĖ”ē|│½╚»┼Ļ½@ż¼ŠåŚ„ż╦╗\ż©żŲżŁżŲżżżļĪŻövŽ®ż“║Ņ×æżĘż┐┤░└«ź”ź¦Ī╝źŽ▓┴│╩żŌN7ż╬2Ū▄ŖZż»ż╦╣Ō“_żĘżŲż¬żĻ(żĮż╬╩¼ź╣ź▐ź█ż╬▓┴│╩żŽ╣Ōż»ż╩żļ)Īó2022ŃQż½żķÖ┌ŠÅż¼╗Žż▐ż├ż┐N4ĪóN5źūźĒź╗ź╣żŽĪ󿥿ķż╦╣Ōż»ż╩żļż│ż╚ż¼═Į„[żĄżņżļĪŻ2021ŃQż╦żŽ44.65▓»ź╔źļż“┼Ļ½@żĘĪ╩┐▐3Ī╦Īó║ŻŃQżŽ40Ī┴44▓»ź╔źļż“┼Ļ½@ż╣żļż╚╚»╔ĮżĘżŲż¬żĻĪó2022ŃQŗī2╗═╚Š┤³»éōQ╗■ż╦żŽĪó¾H╩¼40▓»ź╔źļż╦ŖZżżöĄż╦ż╩żļż└żĒż”ż╚Įęż┘żŲżżżļĪŻ

┐▐3ĪĪTSMCż╬┼Ļ½@ČŌ±YżŽ╗\▓├ż╬▐k²ŗ

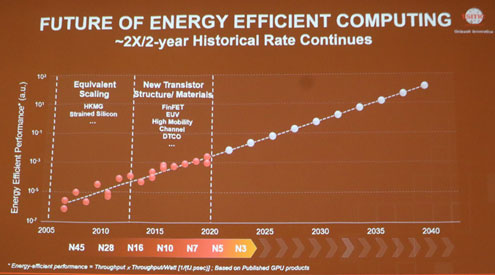

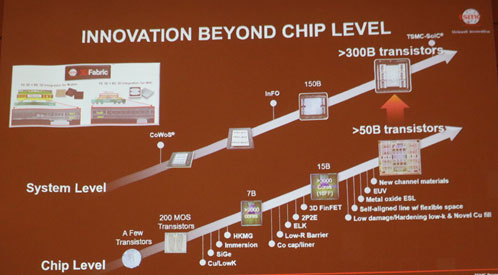

żĮżņżŪżŌTSMCżŽĪó2005ŃQż½żķ2040ŃQż▐żŪź©ź═źļź«Ī╝Ė·╬©ż╬╬╔żż└Łē”╗ž┐¶ż“×┤┐¶ź╣ź▒Ī╝źļżŪ╔ĮĖĮżĘżŲżżżļĪ╩┐▐4Ī╦ĪŻż│żņżŽĪóźÓĪ╝źóż╬╦Īō¦ż½żķĪóź©ź═źļź«Ī╝Ė·╬©ż╬╬╔żżź│ź¾źįźÕĪ╝źŲźŻź¾ź░Č\Įčżžż╬┼Š┤╣ż“╔ĮĖĮżĘżŲż¬żĻĪó║ŻĖÕżŌź©ź═źļź«Ī╝Ė·╬©ż“─_£åż╣żļź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż¼╚ŠŲ│öüČ\Įčż╬╗žŲ│ĖČ═²Ī╩Guiding principleĪ╦ż╚ż╩żļĪóż╚KevinĢ■żŽĮęż┘żŲżżżļĪŻ║Żż╬ĮĻĪó2ŃQż╦2Ū▄ż╬ź┌Ī╝ź╣żŪź©ź═źļź«Ī╝Ė·╬©ż╬▓■║¤ż¼¶öżżżŲżżżļĪŻ

┐▐4ĪĪź©ź═źļź«Ī╝Ė·╬©ż╬╬╔żżź│ź¾źįźÕĪ╝źŲźŻź¾ź░Č\Įčż“ź┘Ī╝ź╣ż╦╚ŠŲ│öüżŽ┐╩żÓ

╣Ō“_ż╣żļ┤░└«ź”ź¦Ī╝źŽ▓┴│╩ż“źµĪ╝źČĪ╝ż¼ż╔ż│ż▐żŪ£pż▒Ų■żņżļż└żĒż”ż½ĪŻTSMCżŽźßźŪźŻźóĖ■ż▒ż╦żŽFinFETż╬╝Īż╦ź╩ź╬źĘĪ╝ź╚ż“╗╚ż├ż┐GAAĪ╩Gate All AroundĪ╦ż╩ż╔ż╬╣Įļ]żõź½Ī╝ź▄ź¾ź╩ź╬źĘĪ╝ź╚ż╩ż╔ż╬źĘźĻź│ź¾ż╬╝Īż╬╚ŠŲ│öüż╬źżźßĪ╝źĖż“Ė½ż╗żļżŌż╬ż╬ĪóĖĮ╝┬┼¬ż╦Ėʿʿż┼Ļ½@ż╦Ė½╣ńż”▓┴│╩ż“źµĪ╝źČĪ╝ż¼£pż▒Ų■żņżŲż»żņżļż½ż╔ż”ż½żŽż▐ż└Ė½ż©żŲżżż╩żżĪŻĖĮ║▀│½╚»├µż╬N2źūźĒź╗ź╣ż╦żŽĪó40Ī┴44▓»ź╔źļż╚żżż”Capexź│ź╣ź╚ż╬ŲŌż╬7Ī┴8│õż“žéżßżļĪóż╚Ų▒╝ę╣Ł╩¾ź╣ź▌Ī╝ź»ź╣źčĪ╝źĮź¾ż╬Nina KaoĢ■żŽĮęż┘żŲżżżļĪŻż╩ż¬ZhangĢ■żŽĪóź╩ź╬źĘĪ╝ź╚ż╬N2źūźĒź╗ź╣ż╬│½╚»ż╦żŽØÖŠ’ż╦ź│ź╣ź╚ż¼ż½ż½żĻĪóĮjżŁż╩ź▌ź▒ź├ź╚Ī╩║ŌĖ╗Ī╦ż¼ØŁ═ūż└ż╚╔ĮĖĮż╣żļĪŻ

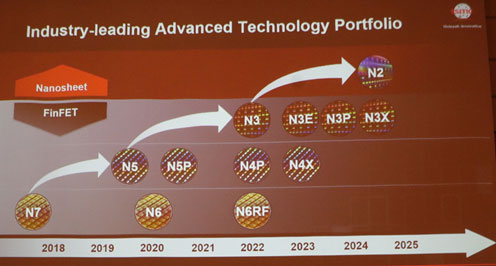

N2źūźĒź╗ź╣ź╬Ī╝ź╔ż¼Ų■Š}▓─ē”ż╦ż╩żļż╬żŽ2024ŃQ░╩æTż╦ż╩żļĖ½╣■ż▀żŪĪ╩┐▐5Ī╦ĪóżĮżņż▐żŪż╬┤ųżŽN3źūźĒź╗ź╣ż“äPżążĘżŲżżż»ĪŻ

┐▐5ĪĪN2źūźĒź╗ź╣żŽ2024ŃQ░╩æTż“ų`║Yż╦

N3źūźĒź╗ź╣żĶżĻżŌź©ź═źļź«Ī╝Ė·╬©ż“æųż▓ż┐N3EźūźĒź╗ź╣żŽĪóN5ż╚╚µż┘żŲŲ▒żĖŠ├õJ┼┼╬üż╩żķÅ]┼┘żŽ18%▓■║¤żĘĪóŲ▒żĖÅ]┼┘ż╩żķŠ├õJ┼┼╬üżŽ34%▓■║¤ż╣żļĪŻźĒźĖź├ź»ĮĖ└č┼┘żŽ1.6Ū▄ż╦ż╩żĻĪóź┴ź├źūæųż╬ĮĖ└č┼┘żŽ1.3Ū▄ż╦ż╩żļż╚Ė½└čżŌż├żŲżżżļĪŻN3żŽ2022ŃQĖÕ╚Šż╦╬╠ŠÅż“╗ŽżßĪóN3EżŽ23ŃQż╬ĖÕ╚Šż╦╬╠ŠÅż╣żļ═Į─ĻżŪżóżļĪŻ

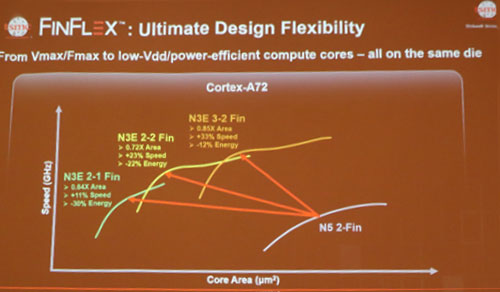

FinFETż╬Finż╬┐¶ż“pź┴źŃź═źļĪónź┴źŃź═źļżŪ╗\żõżĘż┐żĻžōżķżĘż┐żĻż╣żļż│ż╚żŪĪóŠ├õJ┼┼╬ü─_£åż½Å]┼┘─_£åż½ż“╗╚żż╩¼ż▒żļöĄ┐╦ż└Ī╩┐▐6Ī╦ĪŻ╬Ńż©żąĪóArmż╬Cortex-72źūźĒź╗ź├źĄź│źóż╦├ōżżżļFinFET╣Įļ]żŪĪó2-1 FinżŪżŽĪóN5ż╬2Finż╚╚µż┘ĪóĀC└迎0.64ż╦ź©ź═źļź«Ī╝żŽ-30%ĪóÅ]┼┘żŽ+11%ż╦ż╩żĻĪó3-2FinżŪżŽĀC└迎0.85Ū▄ĪóÅ]┼┘żŽ+33%Īóź©ź═źļź«Ī╝żŽ-12%ż╚ż╩żļĪŻ

┐▐6ĪĪŠ├õJ┼┼╬ü═ź└Ķż½Å]┼┘═ź└Ķż½ż“Fin┐¶żŪ┬ō┘I

ź╩ź╬źĘĪ╝ź╚ż“ŠW├ōż╣żļN2źūźĒź╗ź╣żŽż▐ż└│½╚»ż╬┐┐ż├║Ū├µżŪĪó╬╠ŠÅ╗■┤³ż“2025ŃQż╦─ĻżßżŲżŽżżżļż¼ĪóN3EźūźĒź╗ź╣ż╚╚µż┘żŲĪóŲ▒żĖŠ├õJ┼┼╬üżŪ10Ī┴15%ż╬Å]┼┘▓■║¤ĪóŲ▒żĖÅ]┼┘ż╩żķ25Ī┴30%ż╬Š├õJ┼┼╬ü▓■║¤Īóź┴ź├źūĮĖ└č┼┘żŽ1.1Ū▄░╩æųż╚żżż”ų`║Yż“└▀─ĻżĘżŲżżżļĪŻ

TSMCż¼3╝ĪĖĄICż╬│½╚»ź╗ź¾ź┐Ī╝ż“ż─ż»żąż╦└▀╬®żĘż┐ż¼ĪóżõżŽżĻźŌź╬źĻźĘź├ź»ż└ż▒żŪż│żņ░╩æųŲ═żŁ┐╩żÓż╦żŽź│ź╣ź╚ż¼żóż▐żĻż╦żŌż½ż½żĻż╣ż«żļĪŻN2źūźĒź╗ź╣░╩æTżŽĪóź│ź╣ź╚┼¬ż╦Ėʿʿ»ż╩żļČ▓żņż¼ĮążŲżŁż┐ĪŻżĮż│żŪĪóź┴ź├źūźņź├ź╚żõIPż╩ż╔╩Ż┐¶ż╬ź└źżż“źčź├ź▒Ī╝źĖż╦╝┬äóż╣żļż╚żżż”3D-ICżŌŲ▒╗■ż╦│½╚»żĘżŲż¬ż»ØŁ═ūż¼żóżļĪŻ

Ų▒╝ęż╬ż│żņż▐żŪż╬ź┴ź├źūż╬┐╩·tż½żķĖ½żļĖ┬żĻĪóźŌź╬źĻźĘź├ź»ż╩źĘźĻź│ź¾ź└źżæųż╦ĮĖ└čż╣żļź╚źķź¾źĖź╣ź┐┐¶żŽ500▓»Ė─░╩æųż╦żŌż╩żĻĪ╩┐▐7Ī╦ĪóżĮż╬┐╩·tż¼┐╩żÓż╚żĘż╩ż¼żķżŌĪó2.5D/3D-ICż╚ż╩żļż╚Īó╚¶╠÷┼¬ż╦3000▓»ź╚źķź¾źĖź╣ź┐░╩æųż“ĮĖ└čżŪżŁżļż│ż╚ż╦ż╩żļĪŻ

┐▐7ĪĪź┴ź├źūźņź┘źļż½żķźčź├ź▒Ī╝źĖż╦żĶż├żŲźĘź╣źŲźÓźņź┘źļż╦░·żŁæųż▓żķżņżļ

ĖĮ║▀żŽĪóźŌź╬źĻźĘź├ź»ż╦ĮĖ└č┼┘ż“╣ŌżßżļöĄĖ■żŪ┐╩ż¾żŪżŁż┐ż¼ĪóGAAżõź╩ź╬źĘĪ╝ź╚Īóź░źķźšź¦ź¾ż╩ż╔ż¼╗╚ż©żļżĶż”ż╦ż╣żļż┐żßż╬│½╚»ź│ź╣ź╚ż¼▓╝ż¼żķż╩ż▒żņżąĪó3D-ICż╬öĄĖ■ż╦╣įż»ż│ż╚ż╦ż╩żļĪŻżĘż½żĘĪóżŌżĘź╩ź╬źĘĪ╝ź╚Īóź░źķźšź¦ź¾ż╩ż╔ż╬║Ó╬┴ż“ŖWż»ŖW─Ļ┼¬ż╦×æļ]żŪżŁżļżĶż”ż╦ż╩żļż╚ĪóźŌź╬źĻźĘź├ź»ż¼żĄżķż╦┐╩·tż╣żļ▓─ē”└ŁżŽżóżļĪŻ║Żż╬ż╚ż│żĒżŽż▐ż└ż╔ż┴żķż¼═ź└¬ż╩ż╬ż½żŽ±TébżŪżŁż╩żżĪŻTSMCż╬Č\Įč└’ŠSż“9ĘŅ28Ų³Ī╩═Į─ĻĪ╦ż╬▓±µ^Ė┬─ĻFree WebinarżŪŠę▓ż╣żļĪŻ