Nvidiaż¼ASMLĪóTSMCĪóSynopsysż╚┴╚ż▀Īó╝ŖōQĄĪźĻźĮżŪ2nmź╬Ī╝ź╔ż“Ų═Ū╦żž

źūźĒź╗ź╣ź╬Ī╝ź╔2nm░╩æTż╬╝Ī└ż┬Õ╚ŠŲ│öüź┴ź├źū×æļ]ż╦’L(f©źng)ż½ż╗ż╩żżĪó╝ŖōQĄĪźĻźĮź░źķźšźŻĪ╩Computational LithographyĪ╦ż╬ź©ź│źĘź╣źŲźÓż“TSMCż╚NvidiaĪóASMLĪóSynopsysż¼└▀╬®żĘż┐ĪŻ3nmź╬Ī╝ź╔ż╬╝┬ź┴ź├źūæųżŪż╬║ŪŠ«Øó╦Īż¼13nm±śż▐żŪżõż├żŲżŁżŲĪóāS─╣13.5nmż╬EUVźĻźĮżŪżŌOPCĪ╩Ė„ŖZ└▄Ė·▓╠▌ö┘ćĪ╦ż╬Ų│Ų■ż¼’L(f©źng)ż½ż╗ż╩ż»ż╩ż├żŲżŁż┐ĪŻ╝ŖōQĄĪźĻźĮżŽżĮż╬ż┐żßż╬Č\ĮčżŪżóżļĪŻ

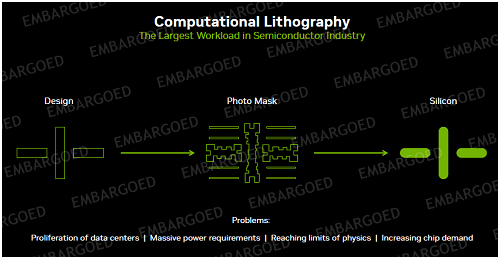

┐▐1ĪĪ╝ŖōQĄĪźĻźĮź░źķźšźŻĪ╩OPCĪ╦ż¼EUVż╦żŌ╗╚ż’żņżļżĶż”ż╦ż╩ż├żŲż»żļĪĪĮąųZĪ¦Nvidia

KrFżõArFźĻźĮź░źķźšźŻżŪ╗╚ż’żņżļźņĪ╝źČĪ╝Ė„ż╬āS─╣żŽĪóżĮżņżŠżņ248nmĪó193nmżŪżóżļż¼Īóż│żņżķż╬āS─╣żĶżĻżŌ╚∙║┘ż╩źčź┐Ī╝ź¾ż“▓├╣®ż╣żļż┐żßOPCČ\Įčż¼╗╚ż’żņżŲżżż┐ĪŻ130nmĪó90nmźūźĒź╗ź╣żŪżŽŲ³╦▄ż¼└ż─cż╬└ĶŲ¼ż╦ż╩ż├żŲOPCČ\Įčż“Ņ~╗╚Īó╬╠ŠÅźūźĒź╗ź╣ż“│╬╬®żĘżŲżŁż┐ĪŻOPCČ\Į迎ĪóArFźĻźĮź░źķźšźŻżŪżŌ╗╚ż’żņżŲżŁż┐ż¼ĪóāS─╣13.5nmż╬EUV╗■┬Õż╦ż╩ż├żŲ║ŲżėOPCČ\Įčż¼╗╚ż’żņżļØŁ═ū└Łż¼ĮążŲżŁż┐ĪŻ╝┬Øó╦Īż╬źčź┐Ī╝ź¾└■╔²ż¼āS─╣ż╚Ų▒żĖ13nm±śż▐żŪ╚∙║┘ż╦ż╩ż├żŲżŁż┐ż½żķż└ĪŻ

┐▐1ż╦┐āż╣żĶż”ż╦╝┬║▌ż╬└▀╝Ŗźčź┐Ī╝ź¾ż“żĮż╬ż▐ż▐╗╚ż├żŲŽ¬Ė„żĘżŲżŌĖ„ż╬Č■└▐żõ╚┐╝o(j©¼)Īóöv└▐ż╩ż╔ż╬▒Ųūxż“£pż▒żŲĪóźĘźĻź│ź¾æųżŪżŽ└▀╝Ŗźčź┐Ī╝ź¾ż“├ķ╝┬ż╦║ŲĖĮżŪżŁż╩żżĪŻż│ż╬ż┐żßĪó║ŪĮ¬┼¬ż╦źĘźĻź│ź¾æųżŪĄßżßżļźčź┐Ī╝ź¾Ę┴ėXż╦ż╩żļżĶż”ż╦Īóź▐ź╣ź»źčź┐Ī╝ź¾żõ░╠┴Ļż“T┘ćż╣żļOPCżõĪóĖ„Ė╗ż╬Ę┴ėXżõź▐ź╣ź»źčź┐Ī╝ź¾ż“║Ū┼¼▓ĮżĘżŲIJ┼└┐╝┼┘ż╩ż╔ż╬źūźĒź╗ź╣ź▐Ī╝źĖź¾ż“▓■║¤ż╣żļ«Ć▓“ćĄČ\Įčż╩ż╔ż¼ØŁ═ūż╦ż╩żļĪŻżĮż│żŪĪóźĘźĻź│ź¾æųż╬╝┬Ę┴ėXż½żķĄšōQżĘżŲźšź®ź╚ź▐ź╣ź»ż╬Ę┴ėXźčź┐Ī╝ź¾ż“╝ŖōQżŪĖ½ż─ż▒żŲż¬ż½ż╩ż»żŲżŽż╩żķż╩żżĪŻż│żņż¼╝ŖōQĄĪźĻźĮź░źķźšźŻż╚Ō}żążņżļČ\Įčż└ĪŻ

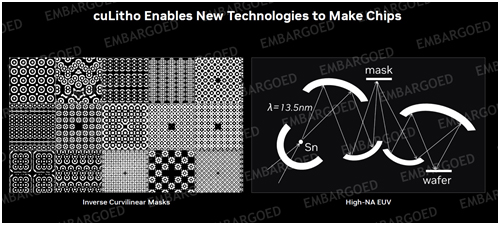

NvidiażŽĪó╝ŖōQĄĪźĻźĮ├ōż╬źĮźšź╚ź”ź¦źócuLithoż╚ĪóGPUż“Įj(lu©░)╬╠ż╦┼ļ║▄żĘż┐╝ŖōQĄĪNvidia DGX H100ż“Ęeż├żŲżżżļż¼Īóż│ż╬╝ŖōQĄĪźĻźĮżŪżŽ500±śż╬H100źĘź╣źŲźÓż“╗╚ż├żŲżżżļĪŻż│żņż▐żŪż╬CPUź┘Ī╝ź╣ż╬╝ŖōQżŪżŽ2ĮĄ┤ųż½ż½ż├żŲżżż┐╝ŖōQ┤³┤ųż“▐k╚šżŪ║čż▐ż╗żļżĶż”ż╩ź╣źįĪ╝ź╔ż╦żŪżŁż┐ĪŻż─ż▐żĻźšź®ź╚ź▐ź╣ź»ż╬öU║Ņż╦ĮĄ┤ųż½ż½ż├żŲżżż┐╗■┤ųż“▐k╚šż╦ø]Į╠żŪżŁżļżĶż”ż╦ż╩ż├ż┐ż╚żżż”ĪŻĄšż╦Ė└ż©żąĪócuLithoż“╗╚ż”╣®ŠņżŪżŽźšź®ź╚ź▐ź╣ź»Īóż╣ż╩ż’ż┴ź┴ź├źū└▀╝Ŗż╬źŲź¾źūźņĪ╝ź╚ż╬Ö┌ŠÅ└Łż¼3Ī┴5Ū▄Ė■æųżĘĪó╝ŖōQż╦ØŁ═ūż└ż├ż┐Š├õJ┼┼╬üż¼1/9ż╦║’žō(f©┤)żŪżŁżļż│ż╚ż╦ż╩żļĪŻ500±śż╬H100źĘź╣źŲźÓżŽĪó4╦³±śż╬CPUźĘź╣źŲźÓż╦┴Ļ┼÷ż╣żļĪóż╚NvidiażŽĖ½└čżŌż├żŲżżżļĪŻ

┐▐2ĪĪ╣ŌNAż╬EUVźĘź╣źŲźÓĪĪĮąųZĪ¦NvidiaĪóASML

ż│ż╬cuLithoż╬ź┴Ī╝źÓżŽĪó“£═ĶCPUżŪ╣įż├żŲżżż┐╝ŖōQĄĪźĻźĮż“GPUżŪ╝ŖōQż╣żļżĶż”ż╦ż╩ż├ż┐ż│ż╚żŪĪ󿥿ķż╩żļ╚∙║┘▓Įż“┐╩żßżļż│ż╚ż¼żŪżŁżļż╚ĪóTSMC╝ęCEOż╬C.C. WeiĢ■żŽ┤³┬įżĘżŲżżżļĪŻŲ▒══ż╦źĻźĮź░źķźšźŻäóÅøż“─¾ČĪż╣żļASML╝ęż╬CEOżŪżóżļPeter WenninkĢ■żŽĪóGPUż╬źĄź▌Ī╝ź╚ż“śO╝ęż╬╝ŖōQĄĪźĻźĮźĮźšź╚ź”ź©źó×æēäż╦┴╚ż▀╣■żÓ╝Ŗ▓ĶżŪżóżĻĪóż│żņż╦żĶż├żŲ╣ŌNAż╬EUVäóÅøĪ╩┐▐2Ī╦ż╬╗■┬Õż¼┐┐╝┬╠Żż“┬ėżėżŲżŁż┐Īóż╚Ėņż├żŲżżżļĪŻż▐ż┐ĪóOPCźĮźšź╚ź”ź¦źóż“─¾ČĪżĘżŲżżżļSynopsysż╬CEOżŪżóżļAart de GeusĢ■żŽĪóĪųNvidiaż╚ź│źķź▄ż╣żļż│ż╚ż╦żĶż├żŲĪóSynopsysż╬OPCźĮźšź╚ź”ź¦źóż“cuLithoæųżŪ┴÷żķż╗żķżņżļż┐żßĪóż│żņż▐żŪ┐¶ĮĄ┤ųż½ż½ż├żŲżżż┐║ŅČ╚ż¼┐¶Ų³żŪżŪżŁżļżĶż”ż╦ż╩żļĪūż╚┤³┬įżĘżŲżżżļĪŻ

ż│ż╬Č\Į迎ĪóNvidia╝ń╠¢ż╬GTC 2023żŪ╚»╔ĮżĄżņż┐ĪŻźķźįź└ź╣żŽ2nmźūźĒź╗ź╣ż½żķ╬╠ŠÅż“╗ŽżßżļöĄ(sh©┤)┐╦żŪżóżļż½żķĪóż│ż╬╝ŖōQźĻźĮź░źķźšźŻČ\Į迎’L(f©źng)ż½ż╗ż╩żżĪŻ║Żövż╬4╝ęż╦żĶżļź│źķź▄źņĪ╝źĘźńź¾ż“ĪóNvidia ż╬ź╦źÕĪ╝ź╣źĻźĻĪ╝ź╣żŪżŽźšźĪź”ź¾źŪĪ╝źĘźńź¾ż╚żżż”Ė└żżöĄ(sh©┤)ż“żĘżŲżżżļĪ╩╗▓╣═½@╬┴1Ī╦ĪŻźķźįź└ź╣żŽż│ż╬źšźĪź”ź¾źŪĪ╝źĘźńź¾ż╦Ų■żņżļż╬ż½ĪóżóżļżżżŽśOżķ╝ŖōQźĻźĮż╬źčĪ╝ź╚ź╩Ī╝źĘź├źūż“║Ņżļż╬ż½Īó┴ßż»żŌ┐ʿʿż▓▌¼öż¼ĮążŲżŁż┐ĪŻ

╗▓╣═½@╬┴

1. "NVIDIA, ASML, TSMC and Synopsys Set Foundation for Next-Generation Chip Manufacturing", Nvidia

(2023/03/21)