ĮjŠ}Ė▄Ąęż½żķÅR╩Ėż“æ]ż┴└┌żķżņżŲżŌĪó┐Ę×æēäżŪ└«─╣ż“äPżąż╣Silego╝ę

ĮjŠ}ż╬Ė▄Ąęż½żķÅR╩Ėż“æ]ż┴└┌żķżņż┐żķż╔ż”ż╣żļż½Ī®IntelĖ■ż▒ż╬ź┴ź├źūż“│½╚»żĘżŲżŁż┐Š«żĄż╩ź┘ź¾ź┴źŃĪ╝ĪóSilego╝꿎Īó4ŃQØiź»źĒź├ź»ź┐źżź▀ź¾ź░ź┴ź├źūż╬ÅR╩Ė─õ┘Vż“╣ż▓żķżņż┐ĪŻż╦żŌż½ż½ż’żķż║ĪóżĘżųż╚ż»żĘż½żŌ└«─╣ż╦╩čż©żŲżŁż┐ĪŻCEOż╬Ilbok LeeĢ■żŽĪóśO╩¼ż╬ć@ØiżŽIlb OKż╚Ų╔żßżąOKż╩ż╬ż└ż½żķĪó┐Ęż┐ż╩Č\Įčż“│½╚»ż╣żņżążżżżĪóż╚Š’ż╦ØiĖ■żŁż└ĪŻ

┐▐1ĪĪSilego╝ęCEOż╬Ilbok LeeĢ■

2001ŃQ┴ŽČ╚ż╬źšźĪźųźņź╣żŪżóżļSilegoĪ╩źĘźņź┤ż╚Ų╔żÓĪ╦żŽĪ󟻟Ēź├ź»ź┐źżź▀ź¾ź░ICż“└▀╝ŖĪóIntelż╦Ū╝żßżļż│ż╚żŪŠå└«─╣żĘżŲżŁż┐ż¼Īó2007ŃQż│żĒż½żķź»źĒź├ź»ICźėźĖź═ź╣żŽŲ¼æ]ż┴ż╦ż╩ż├żŲżŁż┐ĪŻIntelżŽIvy Bridgeż╩ż╔ż╬źūźĒź╗ź├źĄżõżĮż╬╝■╩šż“┤▐żßż┐ź┴ź├źūź╗ź├ź╚ż╬├µż╦ź»źĒź├ź»ICż“ĮĖ└čżĘżŲżĘż▐ż├ż┐ż╬żŪżóżļĪŻź»źĒź├ź»ICż“ŲŌē┼żĘż┐ż┐żßż╦Silegoż╬ź┴ź├źūżŽ╔į═ūż╦ż╩ż├ż┐ĪŻ

ĖĮ╝┬ż╦2007ŃQż½żķ2010ŃQż»żķżżż▐żŪżŽĪóIntelżŌ“£═Ķ×æēäż╬Ö┌ŠÅż“¶öż▒ż╩ż▒żņżąż╩żķż╩żżż┐żßĪóĄ£Č╚żŽźŁĪ╝źūżŪżŁż┐(┐▐2Ī╦ĪŻżĘż½żĘ└«─╣żŽżĘż╩żżĪŻżĮżĘżŲżĮż╬żóż╚żŽÖ┌ŠÅ├µ┘Vż╦╝{żż╣■ż▐żņĪ󟻟Ēź├ź»ICżŽČ╦żßżŲŠ»ż╩ż»ż╩ż├ż┐ĪŻż│ż╬ż┐żßĪó┐Ęż┐ż╩źėźĖź═ź╣ż“╬®ż┴æųż▓ż╩ż▒żņżąż╩ż½ż├ż┐ĪŻ

┐▐2ĪĪźūźĒź░źķź▐źųźļźóź╩źĒź░ż“Šå└«─╣żĄż╗ż┐Silego╝ęĪĪĮąųZĪ¦Silego Technology

żĮż│żŪĪóų`ż“¤²ż▒ż┐ż╬żŽĪóźūźĒź░źķź▐źųźļźóź╩źĒź░ICżŪżóżļĪŻź»źĒź├ź»ź┐źżź▀ź¾ź░ICż╬├ō²ŗżŽźŪźĖź┐źļövŽ®ż└ż¼ĪóżĮż╬└▀╝ŖČ\Į迎źóź╩źĒź░żŪżóżļĪŻż│żņż▐żŪż╬Č\Įč½@ŠÅż“Ö┌ż½żĮż”ż╚żĘż┐ż’ż▒ż└ĪŻŲ▒╝꿎Īó┐ʿʿżČ\Įčż“CMICĪ╩Configurable Mixed Signal ICĪ╦ż╚Ō}ż¾ż└ż¼Īó▓╠ż┐żĘżŲ▌xŠņżŽżóżļż½ĪŻ

┴└ż├ż┐▌xŠņżŽĪó“£═Ķż╩żķźŪźŻź╣ź»źĻĪ╝ź╚żŪövŽ®ż“┴╚ż▐ż╩ż▒żņżąż╩żķż╩ż½ż├ż┐I/O╝■żĻżõż┴żńż├ż╚żĘż┐╝■╩šövŽ®ż╬£pŲ░ŗēäż╚źŪźŻź╣ź»źĻĪ╝ź╚ź╚źķź¾źĖź╣ź┐Īó║YØŹźĒźĖź├ź»ż╩ż╔ż╬1ź┴ź├źū▓ĮżŪżóżļĪŻż│ż”żżż├ż┐övŽ®żŽźūźĻź¾ź╚┤łµ£öüż½żķĖ½żņżąŠ«żĄżżż╚żŽżżż©Īó┐¶cm│迎żóżļĪŻż│ż╬övŽ®ż“1Ī┴2mm│čż╬1ź┴ź├źūż╦ĮĖ└čż╣żļż╬żŪżóżļĪŻ┐¶cm│čż¼1Ī┴2mm│čż»żķżżż╦Š«żĄż»ż╩żļĪŻ

ż│ż╬╚»„[żŽ┼÷ż┐ż├ż┐ĪŻź╣ź▐Ī╝ź╚źšź®ź¾ż╦Ūõżņż┐ĪŻź╣ź▐ź█ż╬║ŪĮjż╬╠õ¼öżŽźąź├źŲźĻÖæ╠┐ż“ūāżąż╣ż│ż╚żŪżóżļĪŻźóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄż╦żŽĄĪē”ż“╗\żõżĘżŲż┐żßĪóŠ├õJ┼┼╬üżŽż╔ż”żĘżŲżŌ╗\ż©żŲżĘż▐ż”ĪŻź╣ź▐ź█ż╬└▀╝ŖŪvżŽŠ»żĘżŪżŌźąź├źŲźĻż“ĮjżŁż»żĘż┐żżż¼ĪóŠņĮĻż¼ż╩żżĪŻż│ż╬ż┐żßźūźĻź¾ź╚┤łż“Īųź│ż╬ÖCĪūż╦ż╣żļż╩ż╔Īóż’ż║ż½ż╩ĀC└čż└ż▒żŪ║čż▐ż╗żļżĶż”ż╦┤ł└▀╝Ŗż╦ÅR╬üżĘżŲżŁż┐ĪŻż│ż│ż╦Silegoż╬ź┴ź├źūż“╗╚ż©żą┤łĀC└čż¼┐¶cm│č╩¼żŽžōżļĪŻż│ż╬╩¼Īóźąź├źŲźĻż“ĮjżŁż»żĘżŲÖæ╠┐ż“ūāżąż╗żļĪŻ

░Ųż╬─ĻĪó┐▐2ż╦żóżļ─╠żĻĪó2010ŃQż▐żŪżŽ“£═Ķż╬ź»źĒź├ź»ICźėźĖź═ź╣ż¼┘M¶öżĘżŲżżż┐ż¼Īó2009ŃQż½żķCMICźėźĖź═ź╣ż“╬®ż┴æųż▓ĪóŠåÅ]ż╦äPżėżŲżżż├ż┐ĪŻż│żņż╦×┤żĘżŲ“£═Ķż╬ź»źĒź├ź»ICżŽ2010ŃQ░╩æTŠåÅ]ż╦Š«żĄż»ż╩ż├ż┐ĪŻ2013ŃQżŽCMICż¼9│õ░╩æųż“žéżßżļżĶż”ż╦ż╩żĻĪó▓±╝꿎Šå└«─╣ż“ā~ż▓żŲżżżļĪŻ

żŪżŽĪóż│ż╬CMICż╚żŽ▓┐ż½ĪŻ┤╦▄┼¬ż╦żŽĪó2010ŃQ5ĘŅż╦Šę▓żĘż┐─╠żĻż└ż¼Ī╩╗▓╣═½@╬┴1Ī╦Īó┼÷╗■ż╚░█ż╩żļ┼└żŽĪó│½╚»źĮźšź╚ż“Į╝╝┬żĄż╗ĪóCMICż╬░╠Åøż┼ż▒ż“£½│╬ż╦żĘż┐ż│ż╚ĪŻżĄżķż╦żŽźĒĪ╝ź╔ź╣źżź├ź┴┐Ę×æēäżŌĮążĘż┐ż│ż╚ż└ĪŻ║ŻövżŽĪó“£═Ķż½żķżóżļGPAK DesignerźĮźšź╚ź”ź©źóź─Ī╝źļż╦ĪóDRCĪ╩źŪźČźżź¾źļĪ╝źļź┴ź¦ź├ź½Ī╝Ī╦ż“▓├ż©ż┐ĪŻŲ▒╝ęż╬FPGAżŽOTPĪ╩One time programmable ROMĪ╦ź┘Ī╝ź╣żŪżóżĻĪó║ŪĮ¬┼¬ż╦żŽźūźĒź░źķźÓż╣żļĪŻövŽ®ż╬└▄¶öŠ“°PżõźšźĻź├źūźšźĒź├źūżõź│ź¾źčźņĪ╝ź┐ż╩ż╔║YØŹźĒźĖź├ź»żŽźĮźšź╚ź”ź©źóźķźżźųźķźĻż╦Ų■ż├żŲż¬żĻĪóź╣ź▒ź▐źŲźŻź├ź»Ų■╬üżŪżŁżļż¼Īó║Żövż╬DRCż╬Ų│Ų■ż╦żĶż├żŲĪóķWżżż┐└▀╝Ŗ┐▐ż“╩¼└ŽĪóź©źķĪ╝ż╦żŽźšźķź├ź░ż“╬®żŲĪóĘ┘╣ż“╚»ż╣żļĪŻż│ż╬źĮźšź╚ż╬Ų│Ų■ż╦żĶż├żŲ└▀╝Ŗż╬Ö┌ŠÅ└Łż¼æųż¼żĻĪóGPAK ICż“╗╚ż├żŲį~├▒ż╩övŽ®ż“└▀╝Ŗż╣żļŠņ╣ńĪó┤Ężņżļż╚20╩¼░╩ŲŌżŪź©źķĪ╝ż╩ż»┤░└«żŪżŁżļż╚żĘżŲżżżļĪŻ

┐▐3ĪĪCMICż╬░╠Åøż┼ż▒ĪĪĮąųZĪ¦Silego Technology

CMICż╬░╠Åøż┼ż▒żŽĪóAlterażõXilinxż╬FPGAż╚░Ńż├żŲż║ż├ż╚övŽ®æä╠Žż¼Š«żĄżżż│ż╚(┐▐3)ĪŻźļź├ź»źóź├źūźŲĪ╝źųźļ┐¶ż╩żķ20 LUTµć┼┘ż└ż╚żżż”ĪŻż│żņż╦×┤żĘżŲĪóSiBlueĪ╩Latticeż╦āA╝²żĄżņż┐Ī╦żŽźŪźĖź┐źļż¼├µ┐┤żŪ▓┴│╩żŌ╣ŌżżĪŻż▐ż┐źóź¾źūżõź│ź¾źčźņĪ╝ź┐ż╬żĶż”ż╩źóź╩źĒź░ĄĪē”żŪżŽĪóŲ▒══ż╦źūźĒź░źķźÓ▓─ē”ż╩Cypress╝ęż╬pSoCż╚░ŃżżĪóź▐źżź»źĒź│ź¾ź╚źĒĪ╝źķż“╗╚ż’ż╩żżĪŻź│źŲź│źŲż╬źŽĪ╝ź╔ź’źżźõĪ╝ź╔övŽ®ż└ż¼Īóźóź╩źĒź░ŗ╩¼ż“į~├▒ż╦└▀╝ŖżŪżŁżļź─Ī╝źļż“×óż©żŲżżżļ┼└ż¼źµź╦Ī╝ź»ż╚Ė└ż©żĶż”ĪŻ

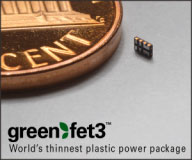

┐▐4ĪĪĖ³żĄ0.27mmż╬źĒĪ╝ź╔ź╣źżź├ź┴ĪĪĮąųZĪ¦Silego Technology

ż│ż╬ż█ż╔┐Ę×æēäż╚żĘżŲĪóźčź’Ī╝FETż“żżż»ż─ż½ĮĖ└čżĘż┐╔ķ▓┘ź╣źżź├ź┴SLG59M1446VżŌźĻźĻĪ╝ź╣żĘż┐ĪŻż│żņżŽĪóż’ż║ż½1.0mmĪ▀1.6mmż╬źčź├ź▒Ī╝źĖż╦╝²═ŲżĘż╩ż¼żķŽó¶ö1Aż╬┼┼╬«ż“╣ŌÅ]ż╦ź╣źżź├ź┴żŪżŁżļICĪŻżĄżķż╦║ŪĮj6Aż╚2Aż╬┼┼╬«ż“└┌żĻü÷ż©żķżņżļnź┴źŃź¾ź═źļźčź’Ī╝MOSFETŠW├ōż╬╔ķ▓┘ź╣źżź├ź┴SLG59M1470Vż╚Īó║ŪĮj2.5Aż╬┼┼╬«ż“└┌żĻü÷ż©żķżņĪóżĘż½żŌĖ³żĄż¼0.27mmż╚£pŲ░ŗēäż╚Ų▒żĖĖ³żĄż╬źčź├ź▒Ī╝źĖLo-Z ETDFNżŌ╚»╔ĮżĘż┐(┐▐4)ĪŻ║ŪĖÕż╬Lo-Zźčź├ź▒Ī╝źĖżŽ╣ŌżĄż¼WLCSPż╬╚Š╩¼ż╦ż╩żļż┐żßĪ󟔟©źóźķźųźļź©źņź»ź╚źĒź╦ź»ź╣żžż╬▒■├ōżŌ£å╠Ņż╦Ų■żņżŲżżżļĪŻ

╗▓╣═½@╬┴

1. ┐ʿʿż▌xŠņ│½¹£ż¼▓─ē”ż╦ż╩ż├ż┐FPGAČ╚─cĪóź┴źŃź¾ź╣ż╚Č╝░ęż¼±é┘T(2) (2010/05/19)