ź╗ź▀ź│ź¾źĖźŃźčź¾2023Īó└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░Č\Įčż¼¶öĮąĪ╩2Ī╦

3D-ICżŪżŽ└čż▀─_ż═żļź┴ź├źūż“ź”ź¦Ī╝źŽ├╩│¼ż½żķŪ÷ż»║’żĻŲDżķż╩ż▒żņżąż╩żķż╩żżż¼Īó“£═ĶżŽĪó╠¾850µmż╬Ė³żĄż╬źĘźĻź│ź¾ź”ź¦Ī╝źŽż╬Įj(lu©░)ŗ╩¼Ī╩90%µć┼┘Ī╦ż“║’ż├żŲ╝╬żŲżŲżĘż▐ż├żŲżżż┐ĪŻ┤─ČŁż╦żŌź│ź╣ź╚┼¬ż╦żŌĄKż½ż├ż┐ĪŻżĮż│żŪź”ź¦Ī╝źŽ╔ĮĀCż“Ū÷ż»żŽż«ŲDż├żŲĪó╗─żĻż“║ŲŠW(w©Żng)├ōż╣żļż╚żżż”╚»„[ż¼ĮążŲżŁż┐ĪŻ2ŗżŪżŽż│żņżķż╚źŲź╣ź┐Ī╝ż╦ż─żżżŲŠę▓ż╣żļĪŻĪ╩ŗī1ŗżŽż│ż┴żķĪ╦

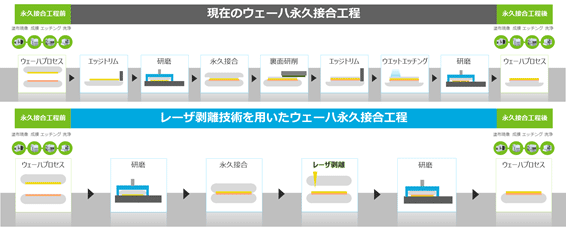

źūźĒź╗ź╣äóÅøż╬äė(d©░ng)żż┼ņ»Bź©źņź»ź╚źĒź¾Ī╩TELĪ╦żŌ└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░Ė■ż▒ż╬×æļ]äóÅøż╦ŲDżĻ┴╚ż¾żŪżżżļĪŻ║Żöv╚»╔ĮżĘż┐ż╬żŽź┴ź├źūż“3╝ĪĖĄ┼¬ż╦└čż▀─_ż═żŲżżż»Šņ╣ńż╦ź┴ź├źūż“Ū÷ż»║’żķż╩ż»żŲżŽż╩żķż╩żżż¼Īó╩¼Ė³żżź”ź¦Ī╝źŽżŪĘ┴└«żĘż┐ICövŽ®ŗ╩¼ż└ż▒ż╬Ė³żĄż└ż▒Ī󟔟¦Ī╝źŽż“żŽż«ŲDż├żŲżĘż▐ż”ż╚żżż”Č\ĮčĪ╩┐▐5Ī╦żŪĪóTELżŽXLOĪ╩Extreme Laser Lift-offĪ╦Č\Įčż╚Ō}ż¾żŪżżżļĪŻ

┐▐5ĪĪ┼ņ»Bź©źņź»ź╚źĒź¾ż╬ź”ź¦Ī╝źŽŁé▀`Č\Įčż╬▐k╬ŃĪĪĮąųZĪ¦┼ņ»Bź©źņź»ź╚źĒź¾

3╝ĪĖĄICżŪżŽĪóICövŽ®ż“Ę┴└«żĘż┐ź”ź¦Ī╝źŽæųż╦Īó╩╠ż╬ź”ź¦Ī╝źŽż“źšź¦źżź╣2źšź¦źżź╣Ī╩face to faceĪ╦żŪĘ┴└«ż╣żļŠņ╣ńĪó╗╚ż’ż╩żżźąźļź»źĘźĻź│ź¾ż“Ė”╦߿ʿŲŪ÷ż»ż╩żļż▐żŪ║’ż├żŲżżż┐ĪŻżĮż╬ĖÕż╬TSVĪ╩Through Silicon ViaĪ╦ż╩ż╔żŪ┐╝żż╣┬ż╦┼┼Č╦ż“Ę┴└«ż╣żļŠņ╣ńż╦Ė³ż▒żņżą║ŅČ╚╗■┤ųż¼ż½ż½żĻż╣ż«żŲżĘż▐ż”ż½żķż└ĪŻ╩¼Ė³żżźĘźĻź│ź¾ż“╝╬żŲżŲżĘż▐ż”ż┐żßĪó╠ĄŠGż¼Ö┌żĖżļż└ż▒żŪżŽż╩ż»żĮż╬ĮĶ═²ż╬ż┐żßż╦ØŁ═ūż╩ź©ź═źļź«Ī╝ż╩ż╔┤─ČŁ╔ķ▓┘ż¼Įj(lu©░)żŁż½ż├ż┐ĪŻ

żĮż│żŪTELż¼│½╚»żĘż┐ż╬żŽĪó╦▄═Ķ║’żĻŲDżļż┘żŁźąźļź»źĘźĻź│ź¾ż╬æųż½żķźņĪ╝źČĪ╝ż“┼÷żŲĪóżĘż½żŌĪó║’żĻŲDżĻż┐żż┐╝żżŗ╩¼ż╦IJ┼└ż“╣ńż’ż╗Ī󟔟¦Ī╝źŽµ£ĀCż╦ź╣źŁźŃź¾ż╣żļż│ż╚żŪĪ󟔟¦Ī╝źŽż“Łéż¼żĘż╚żļĪŻ13Ų³ż╦ź╗ź▀ź│ź¾źĖźŃźčź¾żŪ╣ų▒ķżĘż┐TELż╬ąQ╣ńŠW(w©Żng)█`┬Õ╔ĮŲD─∙╠“╝ę─╣żŽĪ󿎿«ŲDż├ż┐ź”ź¦Ī╝źŽż“║ŲŠW(w©Żng)├ōż╣żļż│ż╚ż“ĖĪŲżżĘżŲż¬żĻĪóż▐ż└╝┬├ō▓Įż▐żŪ╗Ļżķż╩żżż¼│½╚»├µż└ż╚Įęż┘żŲżżżļĪŻ

┐▐6ĪĪEVGroupż¼ź▌ź╣ź┐Ī╝·t┐ā(j©®)żĘż┐ź”ź¦Ī╝źŽŁé▀`äóÅøEVG 850 NanoCleaveż╬▒■├ō╬ŃĪĪ

źņĪ╝źČĪ╝ż╦żĶż├żŲź”ź¦Ī╝źŽż“Ū÷ż»żŽż«ŲDżļČ\Į迎ĪóSiCżõGaNżŪżŌ╣įż’żņżŲżżżļż¼ĪóTELż¼┴└ż├ż┐ż╬żŽ3D-ICżžż╬▒■├ōż└ĪŻż▐ż┐TELż╚Ų▒══ĪóEVGroupżŌŲ▒══ż╬×æļ]äóÅøż“?y©żn)æēä▓ĮżĘżŲż¬żĻĪóź╗ź▀ź│ź¾źĖźŃźčź¾żŪżŌNanoCleaveż╚żżż”ć@Š╬żŪź▌ź╣ź┐Ī╝·t┐ā(j©®)żĘżŲżżż┐Ī╩┐▐6Ī╦ĪŻTELŲ▒══ĪóHBMĪ╩High Bandwidth MemoryĪ╦ż╬żĶż”ż╩źßźŌźĻ└č┴žżõFO-WLPĪ╩Fan Out Wafer Level PackagingĪ╦Īóźżź¾ź┐Ī╝ź▌Ī╝źČĪóźżźßĪ╝źĖź╗ź¾źĄĪóź└źż2ź”ź¦Ī╝źŽĪ╩Die to WaferĪ╦└▄╣ńż╩ż╔ż╬└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░Č\Įčżžż╬▒■├ōż“┴└ż├żŲżżżļĪŻźņĪ╝źČĪ╝ż“Š╚╝o(j©¼)żĘż┐ź”ź¦Ī╝źŽŲŌŗż╬ÕX(qi©ón)żŽ▐kĮų╣Ōča(b©│)ż╦ż╩żļż└ż▒ż╩ż╬żŪĪóIJ┼└ż½żķż║żņżŲżżżļICövŽ®ż╦żŽż█ż╚ż¾ż╔▒Ųūxż“═┐ż©ż╩żżż╚żżż”ĪŻ

└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░Č\Į迎Īó╬╔╚▌╚Į─Ļżõ╝┬╬üż╬▒R─Ļż“╣įż”źŲź╣ź┐Ī╝ż╦żŌ▒Ųūxż“═┐ż©żŲżżżļĪŻźŲź╣ź┐Ī╝ż╬źóź╔źąź¾źŲź╣ź╚żŽĪó2.5D/3D-ICĖ■ż▒ż╬źŲź╣ź╚źŽź¾ź╔źķĪ╝HA1200żõHBMĖ■ż▒ż╬ź┴ź├źūź╣ź┐ź├ź»ĖÕż╬źŲź╣ź┐Ī╝Īó╣ŌĮĖ└čICż╦Ąßżßżķżņżļ╣ŌÅ]Ī”╣Ō┬ė░Ķ╔²Ī”¾Hźįź¾▓Įż╩ż╔ż╦×┤▒■żĘż┐SoCźŲź╣ź┐Ī╝V93000ż╚Č”ż╦╗╚ż”╣ŌÅ]źĘźĻźóźļźżź¾ź┐Ī╝źšź¦źżź╣├ōż╬ź½Ī╝ź╔ĪųPin Scale Multilevel SerialĪūĪ╩┐▐7Ī╦ż“│½╚»żĘżŲżżżļĪŻ

┐▐7ĪĪ╣ŌÅ]źĘźĻźóźļźżź¾ź┐Ī╝źšź¦źżź╣ż╦×┤▒■żĘż┐V93000├ōż╬ź½Ī╝ź╔Ī╩║ĖĪ╦ż╚V93000 EXA ScaleźŲź╣ź┐Ī╝╦▄öüĪĪĮąųZĪ¦źóź╔źąź¾źŲź╣ź╚

Ö┌└«AIżõHPCĪóźĄĪ╝źąĪ╝ż╩ż╔ż╬Ų¼╦Nż╚ż╩żļSoCż╬Ų■Įą╬üIFĪ╩źżź¾ź┐Ī╝źšź¦źżź╣Ī╦żŽż▐ż╣ż▐ż╣╣ŌÅ]ż╦ż╩żļż┐żßĪóżĮżņż╦×┤▒■ż╣żļźŲź╣ź┐Ī╝V93000 EXA Scależ╦║╣żĘ╣■żÓź½Ī╝ź╔Ī╩ź▄Ī╝ź╔Ī╦ż╬ĄĪē”Ī”└Łē”żŽĪó16źņĪ╝ź¾ż╬╩┬š`ż“źŲź╣ź╚żŪżŁĪó║ŪĮj(lu©░)32Gbpsż╬źŪĪ╝ź┐źņĪ╝ź╚ż“Ęeż┴Ī󿥿ķż╦1ż½0ż└ż▒ż╬NRZĪ╩Non Return to ZeroĪ╦┐«ęÄ(gu©®)ż└ż▒żŪżŽż╩ż»Īó┐Č╔²ż╬¾H├═▓Įż“╗╚ż”PAMĪ╩Pulse Amplitude ModulationĪ╦3żõPAM4┐«ęÄ(gu©®)ż╦żŌ×┤▒■ż╣żļĪŻ

3D-ICżŪżŽĪó╬Ńż©żąHBMż╬źŲź╣ź╚ż╩ż╔żŪżŽźĒźĖź├ź»ź”ź¦Ī╝źŽż╬æųż╦ź└źżż“4ĮŚżóżļżżżŽ8ĮŚź╣ź┐ź├ź»żĘżŲżżżļż¼Īóź└źżźņź┘źļżŪ╬╔ēäż└ż╚żĘżŲżŌź╣ź┐ź├ź»ĖÕż╦▓┐żķż½ż╬╔į╬╔ż¼╚»Ö┌żĘżŲżżżļż½żŌżĘżņż╩żżĪŻżĮż╬ż┐żßż╦źŲź╣ź┐Ī╝żŪ╬╔╚▌ż“╚Į─Ļż╣żļØŁ═ūż¼żóżļĪŻźóź╔źąź¾źŲź╣ź╚żŽĪ󟔟¦Ī╝źŽæųżŪHBMż“źŲź╣ź╚żŪżŁżļżĶż”ż╩źŽź¾ź╔źķĪ╝HA1200ż“│½╚»żĘż┐ĪŻż│żņż▐żŪOSATż¼źčź├ź▒Ī╝źĖĖÕż╦źŲź╣ź╚żĘżŲżżż┐╣Óų`ż“µ£żŲź”ź¦Ī╝źŽæųżŪ│╬Ū¦żŪżŁżļżĶż”ż╦żĘżŲżżżļĪŻżĄżķż╦ĪóSoCżŪżŽ─Ļ┼┼░Ą▓Įż¼┐╩ż¾żŪżŽżżżļż¼Įj(lu©░)┼┼╬«▓ĮżŌ├°żĘżżż┐żßĪóß×═Ų╚»ÕX(qi©ón)ż¼ż│żņż▐żŪ1000Wżõ1500Wż▐żŪż╬źŽź¾ź╔źķĪ╝ż¼¾Hż½ż├ż┐ż¼Īó║ŻövĪóźóź╔źąź¾źŲź╣ź╚żŽź¬źūźĘźńź¾ż└ż¼2000Wż▐żŪ×┤▒■żŪżŁżļżĶż”ż╩ča(b©│)┼┘öU(ku©░)ĖµĄĪē”ż“Ęeż┐ż╗ż┐ĪŻ

żĄżķż╦║ŻövżŽNANDźšźķź├źĘźÕźŲź╣ź┐Ī╝ż╚żĘżŲ║ŪĮj(lu©░)1024Ė─ż╬źšźķź├źĘźÕźßźŌźĻź┴ź├źūż“ź”ź¦Ī╝źŽæųżŪŲ▒╗■ż╦▒RżņżļźŲź╣ź┐Ī╝T5230Ī󿥿ķż╦ź”ź¦Ī╝źŽźņź┘źļż╬źąĪ╝ź¾źżź¾ż¼żŪżŁżļ║ŪĮj(lu©░)5.4Gbpsż╬╣ŌÅ]źżź¾ź┐Ī╝źšź¦źżź╣ż“└▀ż▒ż┐ź”ź¦Ī╝źŽźĮĪ╝ź╚ĄĪē”ż“└▀ż▒ż┐T5835Īó║ŪĮj(lu©░)32Gbpsż╬╣ŌÅ]źĘźĻźóźļźżź¾ź┐Ī╝źšź¦źżź╣ż╦×┤▒■żŪżŁżļźčź├ź▒Ī╝źĖż╦╔§┘VżĄżņż┐NANDźšźķź├źĘźÕźßźŌźĻĪ╩ź│ź¾ź╚źĒĪ╝źķŲŌē┼Ī╦żõSSDż╩ż╔ż“źŲź╣ź╚ż╣żļT5851-STM32Gż╩ż╔żŌźĻźĻĪ╝ź╣żĘż┐ĪŻ┐ʿʿżPCIe Gen5ż╩ż╔ż╦×┤▒■żŪżŁżļĪŻżĄżķż╦HBMźŲź╣ź┐Ī╝żŌ│½╚»├µż╬żĶż”ż└ĪŻ