LatticeĪóź╗ź¾źĄ┐«ęÄĮĶ═²ż“Ė½▒█żĘFPGAż╦żŌDSPż“4Ė─┼ļ║▄

Lattice SemiconductorżŽĪóź╣ź▐Ī╝ź╚źšź®ź¾żõź┐źųźņź├ź╚ż╩ż╔ż╬ĄĪē”ż“į~├▒ż╦╗\äėż╣żļż┐żßż╬FPGAż“│½╚»żĘżŲżŁż┐ĪŻ║ŻĖÕż╬ź╣ź▐ź█ż╦┼ļ║▄ż╣żļź╗ź¾źĄż╬┐¶ż¼Ū·╚»┼¬ż╦╗\ż©żļż│ż╚ż“Ė½▒█żĘżŲĪóź╗ź¾źĄ┐«ęÄĮĶ═²├ōDSPż“4Ė─ĮĖ└čżĘż┐FPGAżŪżóżļiCE40 Ultra(┐▐1)ż“×æēä▓ĮżĘż┐ĪŻ

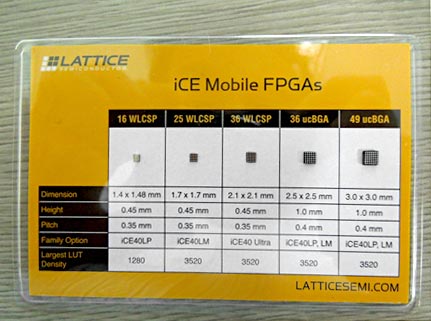

┐▐1ĪĪLatticeż╬Š«æä╠ŽFPGAĪóiCE40źĘźĻĪ╝ź║ĪĪ┐Ę×æē俎┐┐ż¾├µż╬Ultra

Samsung GalaxyźĘźĻĪ╝ź║ż╩ż╔żŪ┬Õ╔ĮżĄżņżļżĶż”ż╦ĪóSamsungż¼1ŃQż╦┐¶ĄĪ¹|żŌż╬ź╣ź▐ź█ż“×æēä▓ĮżŪżŁżļż╬żŽĪóLatticeż╩ż╔ż╬Š«æä╠Žż╩FPGAż“├ōżżżŲ┐ĘĄĪē”ż“╝{▓├żĘżŲżżżļż½żķż└ĪŻźóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄż“║ŅżĻ─Šż╣ż╬ż╩żķ3Ī┴4ŃQż½ż½żļż┐żßĪóźóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄżŽ┘J┘Tż╬ż▐ż▐Īó┐ĘĄĪē”ż└ż▒ż“FPGAż╬źĒźĖź├ź»żŪ╝┬ĖĮż╣żļĪŻLatticeżŽżõżŽżĻŠ«æä╠Žż╩FPGAźßĪ╝ź½Ī╝ż╬Silicon Blue╝ę(╗▓╣═½@╬┴1)ż“2011ŃQż╦āA╝²żĘż┐ż¼Īóż│ż╬Silicon Blueż│żĮĪóSamsungż¼╝ĪĪ╣ż╚┐ĘĄĪ¹|ż“Įąż╣ż┐żßż╬ĖČŲ░╬üż╚ż╩ż├żŲżżż┐ĪŻ

║ŻövĪóLatticeżŽĪóż│ż╬iCE40 Ultraż“├▒ż╩żļLUTĪ╩źļź├ź»źóź├źūźŲĪ╝źųźļĪ╦ż╚SRAMż└ż▒ż╬FPGAżŪżŽż╩ż»Īóż│żņż▐żŪż╬Ęą┘xż½żķØŁ═ūż╚żĄżņż┐ĄĪē”ż“źŽĪ╝ź╔ź▐ź»źĒżŪżŌĮĖ└čżĘż┐ĪŻŠĶōQ▀_Ī”▓├ōQ▀_ĪóĮj┼┼╬«źĘź¾ź»Īó├µ┼┼╬«źĘź¾ź»Ī󟬟ʟņĪ╝ź┐Īó║YØŹI/Oźżź¾ź┐źšź¦Ī╝ź╣ż╩ż╔żŪżóżļ(┐▐2)ĪŻFPGAż╬źĒźĖź├ź»æä╠ŽżŽ║ŪĮj3520Ė─ż╬LUTĪŻ

┐▐2ĪĪ¾H║╠ż╩źŽĪ╝ź╔ź▐ź»źĒż“┼ļ║▄żĘż┐FPGAĪĪØŖż╦4Ė─ż╬DSPżŽź╗ź¾źĄ╗■┬Õż╦×óż©ż┐ĪĪĮąųZĪ¦Lattice Semiconductor

┐▐2ż╬24mA─Ļ┼┼╬«źĘź¾ź»żŽR(śĘ)G(£u)B(×E)3ż─ż╬LEDż“ź╔źķźżźųż╣żļż┐żßż╬övŽ®żŪżóżĻĪó1╦▄ż╬500mAż╚żżż”ĮjżŁż╩─Ļ┼┼╬«ż╬źĘź¾ź»żŽśĘ│░└■źĻźŌź│ź¾ż╦╗╚ż”ż┐żßż╬┼┼╬«Ė╗ż└ĪŻ500mAżŪŅ~Ų░ż╣żņżą10mµć┼┘ż╬š{▀`żŌśĘ│░└■ż“╚¶żąż╗żļż╚żĘżŲżżżļĪŻ

ØŖ╔«ż╣ż┘żŁżŽĪó4Ė─ż╬16źėź├ź╚Ī▀16źėź├ź╚ŠĶōQ▀_ż╚32źėź├ź╚ż╬▓├ōQ▀_ż“ĪóĮĖ└čżĘż┐ż│ż╚ĪŻDSPż╚żĘżŲż╬└čŽ┬▒ķōQżŽżŌż┴żĒż¾ĪóŠĶōQĪó▓├ōQ╩╠Ī╣żŪżŌ╝ŖōQżŪżŁżļĪŻż│ż╬ĄĪē”żŽØŖż╦ź╗ź¾źĄż½żķż╬Įą╬ü┐«ęÄż“ĮĶ═²żĘż┐ĖÕż╦▒ķōQż╣żļż│ż╚ż¼ų`┼¬ĪŻ┐«ęÄĮĶ═²ż╦“£═Ķż╬LUTż“╗╚ż”ż╩żķövŽ®æä╠Žż¼ĮjżŁż»ż╩żĻż╣ż«żļż┐żßĪó└ņ├ōż╬ŠĶōQĪ”▓├ōQ▀_ż“ĮĖ└čżĘż┐ĪŻ╝Ī└ż┬Õż╬ź╣ź▐ź█ż╦┼ļ║▄żĄżņżļĄĪē”ż╦żŽźžźļź╣ź▒źóżõ░╠ÅøĖĪĮąż╩ż╔ż¼żóżĻĪóżĮż╬ż┐żßż╬ź╗ź¾źĄż“¾H┐¶╗╚ż”ż╚Ė└ż’żņżŲż¬żĻĪóżĮżņż╦×┤▒■żĘż┐żŌż╬ĪŻź╗ź¾źĄŠ╩¾ż“ĮĶ═²żĘżŲżżżļ╗■ż╦źóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄżŽĄ┘┘VżĄż╗Š├õJ┼┼╬üż“║’žōżŪżŁżļĪŻ

żĄżķż╦Īóź╣ź▐ź█żõź┐źųźņź├ź╚ż╬Š├õJ┼┼╬üż“║’žōż╣żļż┐żßĪó48MHzż╬ŲŌŗ╚»┐Č▀_ż╦▓├ż©Īó10kHzż╚żżż”─Ń╝■āSż╬╚»┐Č▀_żŌ×óż©żŲż¬żĻĪ󟻟Ēź├ź»ź▓Ī╝źŲźŻź¾ź░ż╦×┤▒■ż╣żļĪŻźĘźĻź│ź¾ż╦ĮĖ└迥żņż┐╚»┐Č▀_żŪżóżļż┐żßĪó╗@┼┘żŽżĮżņż█ż╔╣Ōż»żŽż╩żżż¼Īó│░ŗövŽ®ż╬ź»źĒź├ź»ż╚żĘżŲ╗╚żżĪóźĘź╣źŲźÓµ£öüż╬┼┼╬üż“žōżķż╣ż│ż╚żŌżŪżŁżļĪŻ

![┐▐3ĪĪ▓├Å]┼┘╝Ŗż“ź”ź¦źóźķźųźļĄĪ▀_(│½╚»ź▄Ī╝ź╔)ż╦┼ļ║▄żĘżŲ╩Ō┐¶╝Ŗż╦▒■├ōżĘż┐╬Ń](/archive/editorial/technology/img/TFC140730-01c.jpg)

┐▐3ĪĪ▓├Å]┼┘╝Ŗż“ź”ź¦źóźķźųźļĄĪ▀_(│½╚»ź▄Ī╝ź╔)ż╦┼ļ║▄żĘżŲ╩Ō┐¶╝Ŗż╦▒■├ōżĘż┐╬Ń

╩Ō┐¶╝Ŗż“┐╚ż╦ŠÆż▒ż╩ż¼żķĪóź╣ź▐ź█żŪ╩Ō┐¶ż“ćĶ▒Rż╣żļźŪźŌż“┐āżĘż┐ĪŻ╝┬║▌ż╦Īó│½╚»ź▄Ī╝ź╔ż“Ę╚┬ė├ōż╬ĄĪ▀_ż╦ŲDżĻ¤²ż▒Īóź╣ź▐ź█żžBluetooth SmartżŪźŪĪ╝ź┐ż“┴„żļĪŻ┐▐3ż╬│½╚»Ūvż¼║ĖŠ}ż╦Ęeż─│½╚»ź▄Ī╝ź╔ż╦╩Ō┐¶╝Ŗż“┴╚ż▀╣■ż▀ĪóīÜŠ}ż╬ź╣ź▐ź█żŪźŪĪ╝ź┐ż“£pż▒ŲDżļĪŻ║ĖŠ}ż“āeż╦┐Čżļż╚╩Ō┐¶ż“ź½ź”ź¾ź╚ż╣żļĪŻż│ż╬ź╣ź▐ź█żŪżŽĖ½ż┼żķżżż¼59╩Ōż“┐āżĘżŲżżżļĪŻż│ż╬╩Ō┐¶╝Ŗż╬╗@┼┘ż“æųż▓żļż┐żßĪó▓├Å]┼┘ź╗ź¾źĄżŽæų▓╝öĄĖ■ż╦żŽ┤Čē¶ż╣żļż¼Īó▓ŻöĄĖ■ż╬Ų░żŁż╦żŽ╚┐▒■żĘż╩żżĪŻĖĒż├ż┐Ų░żŁż“╩Ō┐¶ż╚żĘżŲź½ź”ź¾ź╚żĘż╩żżżĶż”ż╦└▀╝ŖżĘżŲżżżļż╚żżż”ĪŻ

iCE40 UltrażŽĪóŲ▒żĖżĶż”ż╩źĒźĖź├ź»æä╠ŽżŪ“£═Ķż╬iCE40 LP(┐▐1ż╬īÜż½żķ2╚ųų`)ż╚╚µż┘żļż╚Š├õJ┼┼╬«żŽ360µAż½żķ1/4ż╬90µAż╦║’žōżĘżŲżżżļĪŻźūźĒź╗ź╣ź╬Ī╝ź╔żŽ40nmĪ󟔟¦Ī╝źŽźņź┘źļCSPźčź├ź▒Ī╝źĖ╔§┘VĪŻźĒźĖź├ź»övŽ®żõŠĶōQ▀_ż╬ĘĖ┐¶źūźĒź░źķź▀ź¾ź░ż╩ż╔ż╬│½╚»ź─Ī╝źļĪóiCE Cube2 ver.2-14-04║Ū┐Ę╚Ūż“╠Ą╬┴żŪź└ź”ź¾źĒĪ╝ź╔żŪżŁżļĪŻ

╗▓╣═½@╬┴

1. ź╣ź▐ź█żõź┐źųźņź├ź╚ż╬┐ĘĄĪē”╝{▓├ż“FPGAżŪźĄź▌Ī╝ź╚ż╣żļźĘźĻź│ź¾źųźļĪ╝ (2011/07/19)