┼ņ»BĖ▐åĶż╬ØŹ×ó╦³├╝XilinxĪóźóź»ź╗źķźņĪ╝ź┐ź½Ī╝ź╔żõ╝Ī└ż┬ÕVERSAL├ō┴T

Xilinxż¼┼ņ»Bź¬źĻź¾źįź├ź»/źčźķźĻź¾źįź├ź»żõĮj(lu©░)żŁż╩ź│ź¾źĄĪ╝ź╚ż╬żĶż”ż╩Įj(lu©░)żŁż╩źżź┘ź¾ź╚ż╦×óż©żŲĪó4K/8KżŪØÖ(r©┤n)░ĄĮ╠Ī”░ĄĮ╠ż╬źėźŪź¬┼┴┴„ż¼▓─ē”ż╩FPGAźĮźĻźÕĪ╝źĘźńź¾ż“ØŹ×óżĘż┐ĪŻGPUżĶżĻżŌ╣ŌÅ]ż╚żżż”źóź»ź╗źķźņĪ╝ź┐ź½Ī╝ź╔ALVEOżõ19ŃQĮą▓┘═Į─Ļż╬VERSALĪ╩╗▓╣═½@╬┴1Ī╦ż╩ż╔żŪĪó100Gbps Ethernetż╩ż╔ż╦×┤▒■ż╣żļĪŻ

┐▐1ĪĪXilinx╝ęČ╚ē»├ōĪ”źųźĒĪ╝ź╔źŁźŃź╣ź╚Ą£Č╚ŗ╠ńźŪźŻźņź»ź┐ż╬Ramesh IyerĢ■(hu©¼)

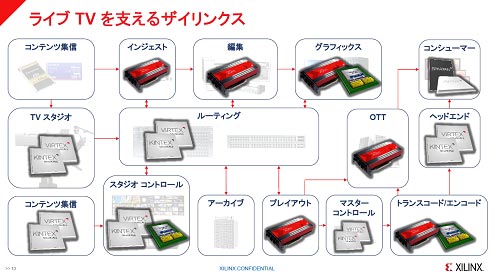

4K/8Kż╬źėźŪź¬┼┴┴„Č\Į迎╩³┴„Č╔ż└ż▒ż╬żŌż╬żŪżŽż╩żżĪŻĮj(lu©░)æä╠Žż╩ź╣ź┐źĖźóźÓżõź│ź¾źĄĪ╝ź╚ź█Ī╝źļżŪż╬Ö┌▒Ū楿“żĮż╬ŠņżŪĖ½ż╗ż┐żĻĪóźŪźĖź┐źļźĘź═ź▐żŪźėźŪź¬ż“╬«żĘż┐żĻż╣żļŠņ╣ńż╦żŌźĘźĻźóźļ┼┴┴„ż╦’L(f©źng)ż½ż╗ż╩żżSerDesĪ╩─Š╩┬š`╩č┤╣Ī╦ź┴ź├źūż¼ØŁ═ūż└ż¼ĪóXilinxżŽżĮż╬ż┐żßż╬ź┴ź├źūżõ░ĄĮ╠ż╣żļż┐żßż╬ź│Ī╝źŪź├ź»ż╩ż╔ż╬ĄĪē”ż“─¾ČĪż╣żļĪŻż│ż╬ż█ż╔═ĶŲ³żĘż┐Ų▒╝ęČ╚ē»├ōĪ”źųźĒĪ╝ź╔źŁźŃź╣ź╚Ą£Č╚ŗ╠ńźŪźŻźņź»ź┐ż╬Ramesh IyerĢ■(hu©¼)(┐▐1)żŽĪóĪųźŲźņźė╩³┴„żõźėźŪź¬ź½źßźķżŪŲ³╦▄żŽ╬╔żż▌xŠņżŪżóżĻĪó╦▄┼÷ż╦źżź▐Ī╝źĘźųż╩öü┘xĪ╩Truly immersive experienceĪ╦ż“╝┬ĖĮż╣żļČ\ĮčżŪ║Ū└Ķ├╝ż“╣įż»Īūż╚═ĶŲ³żĘż┐═²Įy(t©»ng)ż“Įęż┘żļĪŻ

źėźŪź¬┼┴┴„żŪżŽĪó┬ė░Ķż“ż│żņż▐żŪ░╩æųż╦╣Łż▓ż┐żĻĪó░█ż╩żļ░ĄĮ╠öĄ(sh©┤)╝░ż╬ź│Ī╝źŪź├ź»Ī╩ź╚źķź¾ź╣ź│Ī╝źŪź├ź»Ī╦ż“╗╚ż├ż┐żĻż╣żļż╩ż╔ż╬Č\Įčż¼’L(f©źng)ż½ż╗ż╩żżĪŻ╬Ńż©żą╩³┴„Č╔żŪżŽ┤╦▄┼¬ż╦ØÖ(r©┤n)░ĄĮ╠ż╬źėźŪź¬ż“╬«ż╣ż’ż▒ż└ż¼Īó4Kźšź®Ī╝ź▐ź├ź╚żŪ60źšźņĪ╝źÓ/╔├(fps)ż└ż╚10Gbpsż╬┼┴┴„źņĪ╝ź╚ż¼ØŁ═ūż└ż¼Īó8KżŪżĄżķż╦źšźņĪ╝źÓźņĪ╝ź╚ż¼æųż¼żļż╚100Gbpsż╦żŌ×┤▒■żĘżŲż¬ż»ØŁ═ūż¼żóżļĪŻż│ż│żŪżŽXilinxż╬FPGAżõSoCż“żŽżĖżßĪóźóź»ź╗źķźņĪ╝ź┐ź½Ī╝ź╔ż╩ż╔żŌīÖ├ōżĘżŲĪóźėźŪź¬┼┴┴„ż“╝┬ĖĮżŪżŁżļ(┐▐2)ĪŻż▐ż┐╩³┴„Č╔źņź┘źļżŪżŽż╩żż▒■├ōżŪżŽĪóH.264/H.265ż╩ż╔ż╬ź│Ī╝źŪź├ź»żõĪó╩č┤╣²ŗ├µż╬źßźČź╦ź¾ź│Ī╝źŪź├ź»ż╩ż╔żžż╬╩č┤╣Ī”Ąš╩č┤╣ż╦ż╣żļŠņ╣ńżŪżŌ╣ŌÅ]ż╬źĘźĻźóźļ┼┴┴„żŪ┴„żķż╩ż▒żņżąż╩żķż╩żżĪŻ

┐▐2ĪĪźķźżźųTVż╬ź│ź¾źŲź¾ź─║Ņ└«ż½żķŪ█┐«ż╦╗ĻżļżĄż▐żČż▐ż╩╣®µćżŪXilinxż╬ź┴ź├źūż¼╗╚ż©żļĪĪĮąųZĪ¦Xilinx

źėźŪź¬źßźŌźĻżŪżŽDDR4żõDDR5żŪżŽ×┤▒■żŪżŁż╩ż»ż╩żļż┐żßĪó8K╗┼══ż╚╣Ō╗@║┘ż╦ż╩żļż╚Īó3╝ĪĖĄ ICż╬▐k¹|żŪżóżļHBMĪ╩High Bandwidth MemoryĪ╦żŽØŁ┐▄ż╚ż╩żļĪŻHBMż“├ō┴TżĘżŲż¬ż▒żą1ź┴źŃź¾ź═źļ╩¼ż└ż▒żŪżŽż╩ż»Īó┐¶ź┴źŃź¾ź═źļż╬źėźŪź¬┼┴┴„ż¼▓─ē”ż╦ż╩żļĪŻ8Kż╬╣ŌÅ]źĘźĻźóźļ┼┴┴„ż“╝┬ĖĮż╣żļSerDesżŽASICż“ÅŚż│ż╣żĶżĻżŌFPGAż╬öĄ(sh©┤)ż¼ø]Ū╝┤³żŪ╝┬ĖĮżŪżŁżļĪŻ

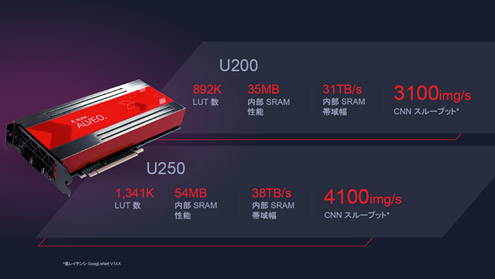

╣ŌÅ]▒ķōQż“źĄź▌Ī╝ź╚ż╣żļźóź»ź╗źķźņĪ╝ź┐ź½Ī╝ź╔ALVEO(┐▐3)żŽĪóPCIeź½Ī╝ź╔żŪżóżĻĪóź│ź¾źįźÕĪ╝ź┐ź▄Ī╝ź╔ż╦żĮż╬ż▐ż▐┘Uż╗żļżĶż”ż╦ż╩ż├żŲżżżļĪŻ▒ķōQ└ņ├ōż╬ź½Ī╝ź╔ż╚żĘżŲźŽĪ╝ź╔ź”ź©źóżŪ╣Į└«żĘżŲżżżļż┐żßĪóCPUżõGPUżĶżĻżŌ╣ŌÅ]żŪżóżļż╚ż▀żŲżĶżżĪŻ

┐▐3ĪĪXilinxż╬źóź»ź╗źķźņĪ╝źĘźńź¾ź½Ī╝ź╔AlveoĪĪCNNżŪż╬ź╣źļĪ╝źūź├ź╚żŽ4100ĮŚ/╔├ĪĪĮąųZĪ¦Xilinx

IyerĢ■(hu©¼)żŽĪóĪųźķźżźųTV├µ┘M(f©©i)żõźŪźĖź┐źļźĘź═ź▐ż╬║Ņ└«ż½żķ£ÉŠ▐ż╦╗Ļżļż▐żŪ╣ŁżżFPGAź┘Ī╝ź╣ż╬×æēäż¼┬Ęż├żŲżżżļĪŻż▐ż┐Īóź│ź¾źĄĪ╝ź╚żõź╣ź▌Ī╝ź─ź╣ź┐źĖźóźÓżŪż╬źżź▐Ī╝źĘźųż╩Ī╩╦ūŲ■┤Č╦■║▄ż╬Ī╦źżź┘ź¾ź╚ż╩ż╔źėźŪź¬┼┴┴„ż╬żĄż▐żČż▐ż╩źĘĪ╝ź¾ż╦╗╚ż©żļ×æēäżŌ┬Ęż©żŲżżżļĪūż╚Įęż┘żŲżżżļĪŻ

╗▓╣═½@╬┴

1. XilinxĪó«Ć╣ŌĄķ2.5D-LSIż╬µ£╦Ųż“£½żķż½ż╦ (2018/10/12)