MicronĪó24Gźėź├ź╚ż╬DRAMź└źżż“TSVżŪ8ĮŚź╣ź┐ź├ź»żĘż┐24GB HBM3ż“Įą▓┘

Micron Technologyż¼źßźŌźĻ═Ų╬╠24GBĪ╩ź«ź¼źąźżź╚Ī╦żŪĪó┼Š┴„źņĪ╝ź╚Ī╩źąź¾ź╔╔²Ī╦1.2TB/sż╚żżż”ĄĮjż╩HBMĪ╩High Bandwidth MemoryĪ╦źßźŌźĻż“│½╚»Ī󟥟¾źūźļĮą▓┘ż“│½╗ŽżĘż┐ĪŻż│ż╬HBM3 Gen2ż“│½╚»żĘż┐═²Įy(t©»ng)żŽĪóÖ┌└«AIż╬│žØ{ż╦Ė■ż▒Īó│žØ{╗■┤ųż╬ø]Į╠ż“┴└ż├ż┐ż┐żßż└Īóż╚Ų▒╝ęź│ź¾źįźÕĪ╝ź╚&ź═ź├ź╚ź’Ī╝źŁź¾ź░Ą£Č╚ŗ╠ń VP Ę¾ ź╝ź═źķźļĪ”ź▐ź═Ī╝źĖźŃĪ╝ż╬Praveen VaidyanathanĢ■żŽĖ└ż”ĪŻ

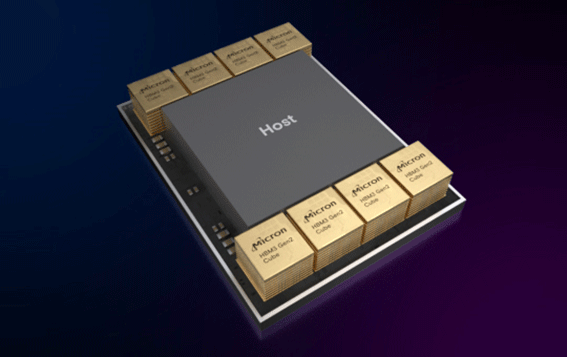

┐▐1ĪĪ│½╚»żĘż┐HBM3 Gen2źßźŌźĻżŽźūźĒź╗ź├źĄż╚ź╗ź├ź╚żŪ╗╚ż”ż│ż╚ż¼¾HżżĪĪĮąųZĪ¦Micron Technology

Ų▒Ģ■ż╦żĶżļż╚ĪóĮjæä╠ŽĖ└ĖņźŌźŪźļĪ╩LLMĪ╦ż╬│žØ{ż╦ĪóĄĮjż╩═Ų╬╠żŪ╣ŌÅ]ż╬┼Š┴„źņĪ╝ź╚ż“Ęeż─ż│ż╬źßźŌźĻż“╗╚ż©żąĪó│žØ{╗■┤ųż“30%ø]Į╠żŪżŁżļż┐żßĪóż│żņż▐żŪ3ź½ĘŅż½ż½ż├żŲżżż┐│žØ{ż¼2ź½ĘŅżŪ║čżÓżĶż”ż╦ż╩żļĪŻÖ┌└«AIż╦ØŁ═ūż╩LLMżŽĪó▓┐╗h▓»ż╚żżż”ĄĮjż╩źčźķźßĪ╝ź┐ż“╗╚ż”ż┐żßĪóżĮżņż╦╣ńż’ż╗ż┐źūźĒź╗ź├źĄż└ż▒żŪżŽż╩ż»ĪóźßźŌźĻżŌżĮżņ┴Ļ▒■ż╬×æēäż¼ĄßżßżķżņżļĪŻż─ż▐żĻĪóĄĮjż╩ź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»ż╬▒ķōQźŪĪ╝ź┐ż“ĮĶ═²ż╣żļźūźĒź╗ź├źĄż╚ĄĮjż╩źßźŌźĻżŽĪó▐kĮ’ż╦┤łż╦╣Į└«żĄżņżļżĶż”ż╦ż╩żļĪ╩┐▐1Ī╦ĪŻ

MicronżŽĪóÖ┌└«AIż╦żĶż├żŲHBMż╬ęŖ═ūżŽż▐ż╣ż▐ż╣╣Ōż▐żĻĪó2022ŃQż½żķ2025ŃQż▐żŪż╬┤ųż╦ŃQ╩┐Čč└«─╣╬©CAGR50%░╩æųżŪ└«─╣ż╣żļż╚═Į▒Rż╣żļĪŻźĄĪ╝źąĪ╝ż╩ż╔ż╬ź│ź¾źįźÕĪ╝ź┐żŽż│żņż▐żŪż╬└@├ōżŪżŽż╩ż»AIż╦ÅR╬üżĘż┐ź│ź¾źįźÕĪ╝ź┐ż╚ż╩żĻĪóźßźŌźĻż¬żĶżėź╣ź╚źņĪ╝źĖ═Ų╬╠żŽĮjżŁż»└«─╣ż╣żļż└żĒż”ż╚Ė½żŲżżżļĪŻ

│½╚»żĘż┐24GBż╬Įj═Ų╬╠żŽĪóĖĮ║▀╬╠ŠÅ├µż╬HBMż╬═Ų╬╠żĶżĻżŌ50%ĮjżŁż»Īó1.2TB/sż╬┼Š┴„źņĪ╝ź╚żŌŲ▒══ż╦ĖĮ║▀╬╠ŠÅ├µż╬HBMżĶżĻżŌ50%Å]żżĪŻż▐ż┐ĪóŠ├õJ┼┼╬ü┼÷ż┐żĻż╬└Łē”żŽĖĮ║▀Ų▒╝ęż╬HBM2eż╚╚µż┘żŲ2.5Ū▄░╩æųż└ż╚żĘżŲżżżļĪŻ

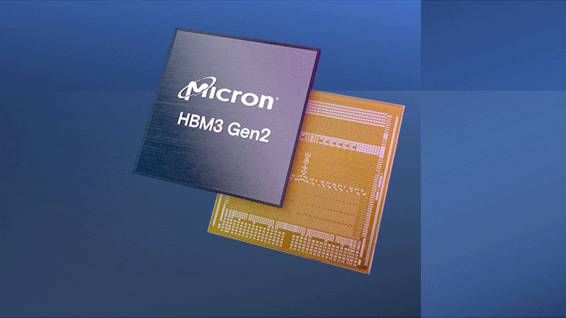

┐▐2ĪĪHBMźßźŌźĻż╬│░Ę┴żŽŲŌŗżŪ8ĮŚź╣ź┐ź├ź»żĘżŲżŌ▐k╚╠ż╬źßźŌźĻ×æēäż╚żĮż”╩čż’żķż╩żżĪĪĮąųZĪ¦Micron Technology

źßźŌźĻ═Ų╬╠ż“╗\żõż╣ż┐żßĪó1β nmźūźĒź╗ź╣Ī╩╗▓╣═½@╬┴1Ī╦żŪ×æļ]żĘż┐24Gźėź├ź╚ż╬DRAMź└źżż“8Ė─ź╣ź┐ź├ź»żĘĪóöUĖµ├ōż╬źĒźĖź├ź»1Ė─ż“ź╣ź┐ź├ź»żĘżŲ╣Į└«żĘż┐ĪŻź└źżŲ▒╗╬ż“└▄¶öż╣żļż┐żßż╦TSV (Through Silicon Via) Č\Įčż“├ōżżż┐ĪŻ“£═Ķż╬HBM3ż╚╚µż┘ĪóTSVż╬┐¶żŽ╠¾2Ū▄Īóźčź├ź▒Ī╝źĖż╬Ū█└■żõŪ█└■┤ų│ųż╩ż╔ż“25%Į╠Š«żĘż┐ż╚żżż”ĪŻ24GB×æēäż╬źčź├ź▒Ī╝źĖźĄźżź║żŽ“£═Ķż╬HBM3ż╚Ų▒żĖ11mmĪ▀11mmĪ╩┐▐2Ī╦ĪŻ1β nmźūźĒź╗ź╣ż╦żĶżļ×æļ]żŽ┼ņ╣ŁćŖ╣®ŠņżŪĪ╩╗▓╣═½@╬┴2Ī╦ĪóTSVż╦żĶżļźčź├ź▒Ī╝źĖź¾ź░żŽ±śŽčżŪ╣įż├żŲżżżļĪŻ

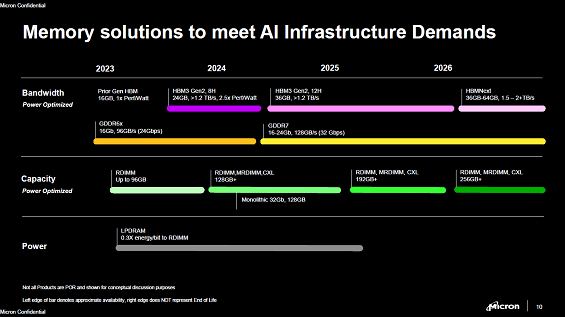

┐▐3ĪĪHBM3 Gen2ż╬źĒĪ╝ź╔ź▐ź├źūĪĪĮąųZĪ¦Micron Technology

MicronżŽ║ŻĖÕż╬HBMż╬źĒĪ╝ź╔ź▐ź├źūżŌ╚»╔ĮżĘżŲż¬żĻĪ╩┐▐3Ī╦Īó═ĶŃQż╦żŽHBM3 Gen2×æēäżŪź╣ź┐ź├ź»żĘż┐8Ė─ż╬DRAMź└źżż╬ź╣ź┐ź├ź»ż½żķ12Ė─ż╬ź└źżż“ź╣ź┐ź├ź»ż╣żļ36GBż╬HBM3 Gen2ż“│½╚»ĪóźĻźĻĪ╝ź╣ż“═Į─ĻżĘżŲżżżļĪŻHBM3ż╬╝ĪżŽHBM3Eż╦ż╩żļż└żĒż”ż╚ĪóVaidyanathanĢ■żŽĖņż├żŲżżżļĪŻ

╗▓╣═½@╬┴

1. ĪųMicronĪó1β nmź╬Ī╝ź╔ż╬64Gźėź├ź╚ż╬DDR5x-DRAMż“źĄź¾źūźļĮą▓┘ĪūĪóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ (2022/11/08)

2. ĪųMicronż╬╣ŁćŖ╣®ŠņĪó1β nm×æēäż╬╬╠ŠÅĮą▓┘ż“Į╦ż”ĪūĪóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ (2022/11/22)