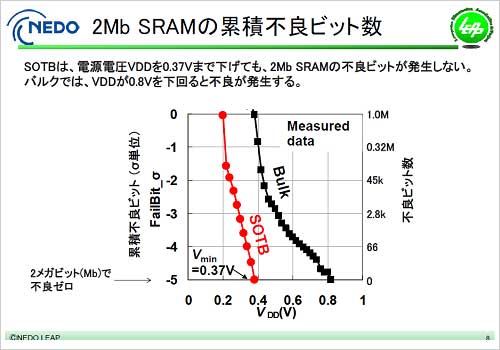

LEAPĪó┼┼Ė╗┼┼░Ą0.37VżŪŲ░ż»2Mźėź├ź╚SRAMż“╗Ņ║ŅĪóµ£źėź├ź╚Ų░║Ņ│╬Ū¦

NEDOĪ╩┐Ęź©ź═źļź«Ī╝ÄźŠÅČ╚Č\Įč┴Ē╣ń│½╚»ĄĪ╣ĮĪ╦ż╚LEAPĪ╩«Ć─Ń┼┼░ĄźŪźąźżź╣Č\ĮčĖ”ē|┴╚╣ńĪ╦żŽĪó0.37Vż╚żżż”─Ńżż┼┼░ĄżŪŲ░║Ņż╣żļSOIż╬MOSFETż“│½╚»(┐▐1)Īó2Mźėź├ź╚ż╬SRAMż“╗Ņ║ŅżĘĪóżĮż╬Ų░║Ņż“│╬Ū¦żĘż┐ĪŻż│ż╬└«▓╠ż“6ĘŅ11Ų³ż½żķ»B┼įżŪ│½╠¢żĄżņżŲżżżļ2013 IEEE Symposium on VLSI Technology and CircuitsĪ╩─╠Š╬VLSI SymposiumĪ╦żŪ╚»╔ĮżĘż┐ĪŻ

![┐▐1ĪĪLEAPż╬─¾░Ųż╣żļSOTBź╚źķź¾źĖź╣ź┐╣Įļ]ĪĪĮąųZĪ¦LEAP](/archive/editorial/technology/img/TFD130612-01a.jpg)

┐▐1ĪĪLEAPż╬─¾░Ųż╣żļSOTBź╚źķź¾źĖź╣ź┐╣Įļ]ĪĪĮąųZĪ¦LEAP

╚ŠŲ│öüLSIż“╚∙║┘▓ĮżĘżŲżżż»ż╚Īóź▓Ī╝ź╚żĘżŁżż┼┼░Ąż╬źąźķż─żŁżŽĮjżŁż»ż╩żļĪŻø]ź┴źŃź¾ź═źļĖ·▓╠ż╚żżż”żĶżĻżŽĪó╔įĮŃرĖČ╗ężĮż╬żŌż╬ż╬┐¶ż¼┐¶Ø▓nm╗═öĄż╚żżż”╚∙║┘ż╩ź╚źķź¾źĖź╣ź┐ōļ░ĶŲŌż╦żĶż├żŲźąźķż─żżżŲż»żļż┐żßż└ĪŻ┼┼Ė╗┼┼░Ąż╬ź▐Ī╝źĖź¾ż“╣Łż»ż╚żļż│ż╚ż¼żŪżŁż╩żżż┐żßĪó┼┼Ė╗┼┼░Ąż“ĮjżŁż»▓╝ż▓żļż│ż╚ż¼żŪżŁż╩żżĪŻź▓Ī╝ź╚┼┼░Ąż╬źąźķż─żŁż¼Š«żĄż▒żņżąĪóŲ░║Ņź▐Ī╝źĖź¾ż“žōżķż╗żļż┐żßĪó┼┼Ė╗ż“▓╝ż▓żŲżŌµ£ź╚źķź¾źĖź╣ź┐ż¼Ų░║Ņż╣żļĪŻ

ź▓Ī╝ź╚żĘżŁżż┼┼░Ąż“»éżßżļźčźķźßĪ╝ź┐ż╬▐kż─ż¼╔įĮŃرĖČ╗ężŪżóżļĪŻżĮżŌżĮżŌźĘźĻź│ź¾ĖČ╗ęż¼1cm3┼÷ż┐żĻ10ż╬24ŠĶĖ─żóżļöü└č├µż╦┤▐ż▐żņżļ╔įĮŃرĖČ╗ę(ź╔ź╩Ī╝żõźóź»ź╗źūź┐)ż¼10ż╬17ŠĶĖ─µć┼┘żóżņżąĪóź╚źķź¾źĖź╣ź┐ż╬┼┼╬«żŽź¬ź¾ż╣żļĪŻż╣ż╩ż’ż┴1000╦³╩¼ż╬1ż╬╔įĮŃرżŪŲ░║Ņż╣żļż╬ż¼╚ŠŲ│öüMOSź╚źķź¾źĖź╣ź┐żŪżóżļĪŻ

ż╚ż│żĒż¼Īóź╚źķź¾źĖź╣ź┐ōļ░Ķż¼20nm╗═öĄż╚ż╩ż├żŲż»żļż╚ĪóżĮż╬├µż╦Ų■żĻż”żļźĘźĻź│ź¾ĖČ╗ęż╬┐¶żŽĪó20nmĪ▀20nmĪß4Ī▀10ż╬-12ŠĶĖ─/cm2ż╚ż╩żļĪŻżŽż╩żŽż└═╦Įż╩Ą─ébż“ż│żņż½żķżĘżŲżżż»ż¼ĪóżŌżĘź╔ź╩Ī╝Ū╗┼┘ż¼10ż╬17ŠĶĖ─/cm3ż└ż╚▓Š─Ļż╣żļż╚Īó├▒░╠╔ĮĀCæųż╦żŽ10ż╬11ŠĶĖ─/cm2ż╬ź╔ź╩Ī╝ż¼ĖĮżņżļż╚╣═ż©żķżņżļĪŻźĘźĻź│ź¾ĖČ╗꿎├▒░╠╔ĮĀCæųż╦10ż╬16ŠĶĖ─żóżļż╚żĘżŲĪó20nmĪ▀20nmŲŌż╦żŽźĘźĻź│ź¾ĖČ╗꿎4Ī▀10ż╬4ŠĶĖ─żóżļż¼Īóź╔ź╩Ī╝ĖČ╗꿎0.4Ė─żĘż½ż╩żżĪŻż─ż▐żĻĪó20nmĪ▀20nmż╬├µż╦żŽ1Ė─żóżļż½0Ė─ż½ż╚żżż”Ą─ébż╦ż╩żļĪŻż│żņżŪżŽĪóź╔ź╩Ī╝ż¼1Ė─żóżļź╚źķź¾źĖź╣ź┐ż╚0Ė─ż╬ź╚źķź¾źĖź╣ź┐ż╦╩¼ż½żņżļż│ż╚ż╦ż╩ż├żŲżĘż▐ż”ĪŻż│ż”ż╩żļż╚ź╚źķź¾źĖź╣ź┐ż╦żĶż├żŲȧĒś┴žż╬─╣żĄżŽĮjżŁż»░█ż╩żĻĪóź▓Ī╝ź╚żĘżŁżż┼┼░ĄżŽĮjżŁż»żążķż─ż»ż│ż╚ż╦ż╩żļĪŻ

ż└ż├ż┐żķżżż├żĮż╬ż│ż╚Īó╔įĮŃرż“Č╦╬üžōżķżĘĪóȧĒś┴žż╬─┤┼Dż“MOSFETż╬┤łźąźżźóź╣żŪ╣įż¬ż”Īóż╚żżż”╣═ż©ż╦├Żż╣żļĪŻż│żņż¼LEAPż╬╣═ż©żļĪóżĘżŁżż┼┼░Ąż╬źąźķż─żŁż“žōżķż╣┤╦▄ĖČ═²żŪżóżļĪŻż┐ż└żĘĪóä▌╣±ż╬╚ŠŲ│öüIPź┘ź¾ź┴źŃĪ╝SuVolta╝ężŌŲ▒══ż╩╣═ż©żŪĪóź▓Ī╝ź╚żĘżŁżż┼┼░ĄVthż╬źąźķż─żŁż“žōżķż╣Č\Įčż“│½╚»żĘĪó╔┘╗╬─╠ź╗ź▀ź│ź¾ź└ź»ź┐Ī╝ż╦źķźżź╗ź¾ź╣ČĪ═┐żĘżŲżżżļĪŻ

║ŻövĪóLEAPżŽĪóØiövĪ╩╗▓╣═½@╬┴1Īó2Ī╦ż╚Ų▒══ĪóSOIĪ╩silicon on insulatorĪ╦╣Įļ]ż╦żĘżŲ┤łźąźżźóź╣ż“ż½ż▒żķżņżļżĶż”ż╦żĘż┐ĪŻMOSź╚źķź¾źĖź╣ź┐żŽĖ³żĄ10nmż╬Ū÷żżļmżß╣■ż▀¤©▓Į╦ņĪ╩BOXĪ╦æųż╦Ę┴└«żĘĪóSOI└õ▒’╦ņż╬┤łŖõż½żķźąźżźóź╣ż“ż½ż▒żķżņżļżĶż”ż╦żĘż┐Ī╩┐▐1Ī╦ĪŻż│ż╬╣Įļ]ż╬SOIź╚źķź¾źĖź╣ź┐ż“LEAPżŽĪóSOTBĪ╩silicon on thin buried oxideĪ╦ź╚źķź¾źĖź╣ź┐ż╚Ō}ż¾żŪżżżļĪŻ

┐▐2ĪĪ┼┼Ė╗┼┼░Ą0.37VżŪ2Mźėź├ź╚SRAMż¼µ£źėź├ź╚Ų░║ŅĪĪĮąųZĪ¦LEAP

ż│ż╬SOTBź╚źķź¾źĖź╣ź┐ż“╗╚ż├żŲ╗Ņ║ŅżĘż┐2Mźėź├ź╚ż╬SRAMżŪ┼┼Ė╗┼┼░Ąż“ż╔ż│ż▐żŪ▓╝ż▓żķżņżļż½ż“─┤ż┘ż┐ĪŻSRAMź╗źļżŽ6Ė─ż╬ź╚źķź¾źĖź╣ź┐ż½żķ└«żĻ╬®ż─źšźĻź├źūźšźĒź├źūż╩ż╬żŪĪóź╚źķź¾źĖź╣ź┐ż¼żążķż─ż»ż╚źßźŌźĻżŽŲ░║ŅżĘż╩ż»ż╩żļĪŻ╝┬┘xżŪżŽĪóŲ░║Ņ┼┼░Ąż“1Vż½żķ▓╝ż▓żŲżżżŁĪó╔į╬╔źėź├ź╚┐¶ż“┐¶ż©ż┐ĪŻż│ż╬±T▓╠Īó┼┼Ė╗┼┼░Ąż“0.37Vż▐żŪ▓╝ż▓żŲżŌSRAMżŽµ£źėź├ź╚Ų░║ŅżĘż┐ĪŻż┐ż└żĘĪóżĮżņ░╩æų▓╝ż▓żļż╚źėź├ź╚╔į╬╔ż“Ö┌żĖżļĪŻŲ▒══ż╦żĘżŲ“£═Ķż╬CMOS╣Įļ]ż╚Ų▒żĖźąźļź»żŪ2Mźėź├ź╚ż╬SRAMż“║Ņżļż╚Īó0.8V░╩▓╝żŪżŽ╔į╬╔źėź├ź╚ż¼Įą╗Žżßż┐ĪŻ

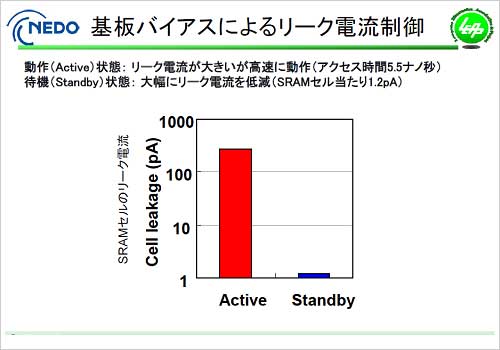

┤łźąźżźóź╣żŽĪóź▓Ī╝ź╚żĘżŁżż┼┼░Ąż“─┤┼DżŪżŁżļż└ż▒żŪżŽż╩ż»Īó┬įĄĪ╗■ż╬źĻĪ╝ź»┼┼╬«ż“═▐ż©żķżņżļż╚żżż”Ė·▓╠żŌżóżļ(┐▐3)ĪŻź▓Ī╝ź╚┼┼░Ą░╩▓╝ż╬źĮĪ╝ź╣-ź╔źņźżź¾┼┼╬«Īóż╣ż╩ż’ż┴źĄźųź╣źņź├źĘźńźļź╔┼┼╬«ż╬ź▓Ī╝ź╚┼┼░Ąż╦×┤ż╣żļ’łżŁż“źĘźŃĪ╝źūż╦ż╣żļż╚żżż”╠“│õż¼┤łźąźżźóź╣ż╦żŽżóżļĪŻż│ż╬ż┐żßĪó╣ŌÅ]Ų░║Ņ╗■ż╚┬įĄĪ╗■żŪ┤łźąźżźóź╣ż“║┘ż½ż»─┤┼Dż╣żņżąĪóLSIµ£öüż╚żĘżŲż╬Š├õJ┼┼╬«ż“▓╝ż▓żļż│ż╚ż¼żŪżŁżļĪŻ

┐▐3ĪĪ┤łźąźżźóź╣żŪźĻĪ╝ź»┼┼╬«ż“▓╝ż▓żļĪĪĮąųZĪ¦LEAP

ż│ż╬SOTBź╚źķź¾źĖź╣ź┐żŽĪóźūźņĪ╝ź╩╣Įļ]ż╬ż▐ż▐╚∙║┘▓ĮżŪżŁżļż╚żżż”źßźĻź├ź╚ż¼żóżļĪŻ┤łźąźżźóź╣żŪźĄźųź╣źņź├źĘźńźļź╔┼┼╬«ż“žōżķż╗żļż½żķż└ĪŻźąźļź»CMOS ż└ż╚Īó10nm±śżžż╚╚∙║┘▓Įż╣żļż╚Īó╩Ż╗©ż╩╣Įļ]ż╬FINFETż╚żżż├ż┐3╝ĪĖĄ╣Įļ]ż¼’Lż½ż╗ż╩żżĪŻSTMicroelectronicsż¼FDĪ╩fully depletionĪ╦Ę┐ż╬SOIź╚źķź¾źĖź╣ź┐żŪżŽFINFETżŽ═ūżķż╩żżż╚Ė└ż├ż┐ż│ż╚ż╚╔õ╣ńż╣żļĪ╩╗▓╣═½@╬┴3Ī╦ĪŻ

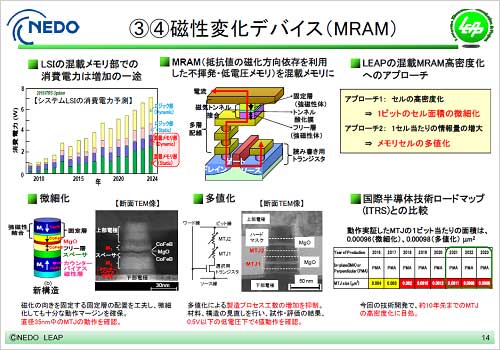

SOTBź╚źķź¾źĖź╣ź┐żŽźĒźĖź├ź»LSI├ōż╦│½╚»żĄżņż┐żŌż╬ż└ż¼ĪóLEAPżŪżŽźßźŌźĻ┴Ū╗ęż╚żĘżŲMRAMĪóPCMĪóĖČ╗ęöĪŲ░źŪźąźżź╣żŌ│½╚»├µż└ĪŻż│ż╬VLSI SymposiumżŪżŽĪóż│żņżķż╬┐╩╩Ōż╦ż─żżżŲżŌ╩¾╣żĘż┐ĪŻMRAMżŪżŽØiövĪ╩╗▓╣═½@╬┴1ż¬żĶżė2Ī╦ż╬─ŠĘ┬50nmźĄźżź║ż╬źßźŌźĻź╗źļż½żķ║ŻövżŽ35nmż╦╚∙║┘▓ĮżĘżŲĪ󿥿ķż╦╔ŌŅ^╝¦Šņż“æ]ż┴Š├żĘ╣ńż”żĶż”ż╦×┤Š╬╣Įļ]ż╦żĘż┐(┐▐4)ĪŻ▓├ż©żŲ¾H├═▓Įż╦ż─żżżŲżŌĖĪŲżżĘĪó2źėź├ź╚/ź╗źļż╬Ų░║Ņż“│╬Ū¦żĘż┐ĪŻ

┐▐4ĪĪMRAMż“╚∙║┘▓ĮżĘĪó2├═▓ĮżŌ╗Ņż▀ż┐ĪĪĮąųZĪ¦LEAP

┴Ļ╩č▓ĮźßźŌźĻĪ╩PCMĪ╦żŪżŽĪó«Ć│╩╗ę╣Įļ]ŲŌżŪż╬GeĖČ╗ęż╬öĪŲ░źßź½ź╦ź║źÓż“▓“£½żĘż┐ĪŻ╣Ō°BŃ^ėX▌åż╬│╩╗ęż╚─Ń°BŃ^ėX▌åż╬│╩╗ęż╚ż╬┤ųż╬╔ÅöĪż╦żŽ±TŠĮż“═Žż½ż╣ż╬żŪżŽż╩ż»Īó┼┼╗ęż╬ÅRŲ■ż╦żĶż├żŲGeĖČ╗ęż╬öĪŲ░ż“śŪ┐╩żĘżŲżżżļż╚żżż”ĪŻ

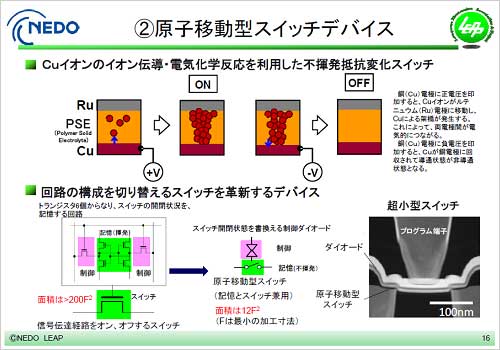

ĖČ╗ęöĪŲ░ź╣źżź├ź┴żŪżŽĪó╔įĦ╚»└Łż╬ĄŁ▓▒┴Ū╗ęż“ź¬ź¾/ź¬źšŲ░║ŅżĄż╗żļ╠“│õż“▓╠ż┐ż╣ź╣źżź├ź┴ź¾ź░ź╚źķź¾źĖź╣ź┐ż“Š«żĄż»ż╣żļż┐żßĪóĄŁ▓▒┴Ū╗ęż╬æųż╦┴ąöĄĖ■ź└źżź¬Ī╝ź╔ż“ź╣źżź├ź┴┴Ū╗ęż╚żĘżŲ└▀ż▒ż┐(┐▐5)ĪŻż│ż╬Šņ╣ńżŽĪóČŌō’-TaO-ČŌō’ż╚żżż”źĘźńź├ź╚źŁź└źżź¬Ī╝ź╔╣Įļ]ż“╗╚żżĪóź└źżź¬Ī╝ź╔ż╬żĘżŁżż┼┼░Ąż“«Ćż╣ż½▒█żĄż╩żżż½żŪź╣źżź├ź┴Ų░║Ņż“╣įż”ĪŻSRAM╣Įļ]ż╬6ź╚źķź¾źĖź╣ź┐öĄ╝░ż╬ĀC└č200F2ż╦×┤żĘżŲĪóż’ż║ż½12F2Ī╩FżŽ║ŪŠ«Øó╦ĪĪ╦żŪż╣ż¾ż└ĪŻ

┐▐5ĪĪ┴ąöĄĖ■ź└źżź¬Ī╝ź╔ź╣źżź├ź┴żŪ╚∙║┘▓Įż╦×┤▒■ĪĪĮąųZĪ¦LEAP

ż│ż╬VLSI SymposiumżŪżŽĪóLEAPż½żķż╬╚»╔Į║╬┘Iéb╩ĖżŽ5°PĪŻż│ż╬┐¶ÖCżŽ║╬┘Iéb╩Ė┐¶1░╠IMECż╬9°Pż╦╝Īż░¾Hżż°P┐¶żŪżóżļĪŻ

╗▓╣═½@╬┴

1. LEAPĪóLSIŠ├õJ┼┼╬ü║’žōż╬ż┐żßż╬MOSż╬Ł∙Vt─ŃžōĪó╔įĦ╚»└ŁźßźŌźĻż╦╬ü┼└ (2012/06/15)

2. LEAPż╬─ŃŠ├õJ┼┼╬üĪ”╔įĦ╚»└ŁźßźŌźĻżŽź╬źżź║ź▐Ī╝źĖź¾╣Łż▓Īó╣ŌĮĖ└č▓Įų`╗žż╣ (2012/12/25)

3. STź▐źżź»źĒż¼źšźĪźųźķźżź╚└’ŠSż“║╬żĻż╩ż¼żķżŌIDMż╦ż│ż└ż’żļ┴└żżż╚żŽ (2013/02/28)