╣ŌĮĖ└迎└▀╝ŖČ\ĮčżŌ║żžMż╦Ī¦└▀╝ŖČ\ĮčįćĪ┴EuroAsia (3)

╣ŌĮĖ└čICżžż╬═ūĄßżŽ┐įżŁż╩żżĪŻżĘż½żŌź│ź╣ź╚æųĖéż“═▐ż©Īó╣Ō└Łē”ż╩Ų╚śOĄĪē”ż“ĮĖ└čżĘĪóŠ├õJ┼┼╬üż“æųż▓ż╩żżĪŻ╣ŌĮĖ└čICż“ż╔ż”żõż├żŲ└▀╝Ŗż╣żļż½ĪŻFPGAźßĪ╝ź½Ī╝żŪżĄż©ĪóICż╬µ£ĄĪē”ż“źūźĒź░źķź▀ź¾ź░ż╣żļż│ż╚ż¼žMżĘż»ż╩ż├żŲżŁż┐ĪŻAlterażŽ▐k╚╠┼¬ż╩CĖ└Ėņż╬OpenCLżŪźūźĒź░źķźÓż╣żļż│ż╚ż“─¾░ŲżĘĪóźŪźČźżź¾źŽź”ź╣ż╬Synapse DesignżŽ└▀╝Ŗ└ņ├ōż╬╝ŖōQĄĪż“│½╚»żĘż┐ĪŻ

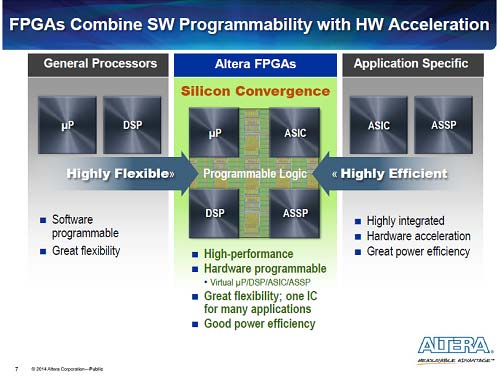

┐▐1ĪĪSoCż╦żŽCPUżõDSPż╬żĶż”ż╩źĮźšź╚ź”ź©źóź┘Ī╝ź╣ź│źóż╚ĪóASICżõASSPż╬żĶż”ż╩└ņ├ōź│źóĪóżĮżĘżŲźūźĒź░źķźÓ▓─ē”ż╩źŽĪ╝ź╔ź”ź©źóövŽ®żŪżóżļFPGAż“Č”┘TżĄż╗żļĪĪĮąųZĪ¦Altera

FPGAż“OpenCLżŪźūźĒź░źķźÓ

AlterażŽ║“ŃQ30╝■ŃQż“Ę▐ż©Īó║Żżõ3000ć@ż╬“£Č╚µ^ż“═╩ż╣żļFPGA┤ļČ╚ż╦ż╩ż├ż┐ĪŻFPGA▐kČ┌żŪżõż├żŲżŁż┐Ų▒╝ęż└ż¼ĪóFPGAż╬źĒźĖź├ź»æä╠Žż¼żóż▐żĻż╦żŌĮj(lu©░)żŁż»ż╩żĻż╣ż«żļż╚źūźĒź░źķź▀ź¾ź░ż╦Įj(lu©░)╩čż╩╗■┤ųż¼ż½ż½żĻżŌżŽżõĖĮ╝┬┼¬żŪżŽż╩ż»ż╩ż├ż┐ĪŻżĮż│żŪĪóźĮźšź╚ź”ź©źóź┘Ī╝ź╣ż╬CPUżõDSPż╚Īó└ņ├ōIPź│źóĪóżĮżĘżŲźŽĪ╝ź╔ź”ź©źóź┘Ī╝ź╣ż╬źūźĒź░źķź▐źųźļźĒźĖź├ź»ż“Č”┘TżĄż╗żļöĄ(sh©┤)╝░ż╬SoCżž┬Õż’żĻż─ż─żóżļ(┐▐1)ĪŻż│ż╬öĄ(sh©┤)╝░ż└ż╚Īóæä│╩ż¼└õż©ż║┬Õż’żļżĶż”ż╩övŽ®żŽźĮźšź╚ź”ź©źóżŪĪó»éż▐ż├ż┐övŽ®ż“╣ŌÅ]ż╦żĘż┐żżŠņ╣ńż╦żŽ└ņ├ōIPż“Īó╣ŌÅ]övŽ®ż“źšźņźŁźĘźųźļż╦╩čż©ż┐żżŠņ╣ńżŽFPGAż“╗╚żż╩¼ż▒Īóø]żż│½╚»┤³┤ųżŪ└▀╝ŖżŪżŁżļżĶż”ż╦ż╩żļĪŻ

Ų▒╝꿎Ī󟎟żź©ź¾ź╔ż╬▒■├ōż╚żĘżŲźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╦ż¬żżżŲĪó▐k─Ļż╬╝ŖōQż“╣ŌÅ]ż╦ĮĶ═²ż╣żļż┐żßż╦ĪóFPGAż╬ŠW(w©Żng)├ōż“─¾░ŲżĘżŲżżżļĪŻĖĪ║„źóźļź┤źĻź║źÓż“║Ū┼¼▓ĮżĘż┐żĻĪóCPUż“╩┬š`Ų░║ŅżĄż╗żļż┐żßż╬źóźļź┤źĻź║źÓż“╝┬╣įżĘż┐żĻż╣żļŠ}├╩ż╚żĘżŲż╬FPGAżŪżóżļĪŻżĮż╬±T▓╠ĪóĖĪ║„ĄĪē”żŪżŽ10Ū▄Īó▓ĶćĄĮĶ═²żŪżŽ9Ū▄ĪóżĮżĘżŲČŌ═╗┤žĘĖż╬╝ŖōQĪ╩ź╣ź╚ź├ź»ź¬źūźĘźńź¾ż╬├═¤²ż▒żõźŌź¾źŲź½źļźĒźĘź▀źÕźņĪ╝źĘźńź¾ż╩ż╔Ī╦żŪżŽ25Ū▄żŌ╣ŌÅ]ż╦ż╩ż├ż┐ż╚żĘżŲżżżļĪŻ

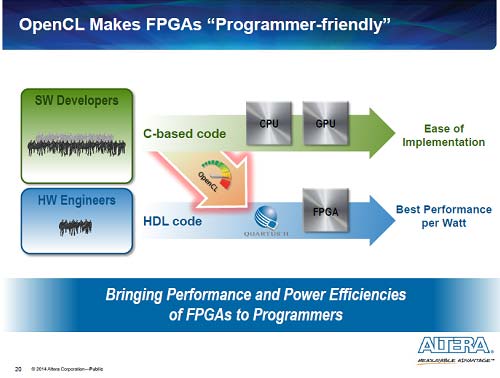

┐▐2ĪĪCPUżõDSP│½╚»ż╦CĖ└Ėņż“╗╚ż├żŲżŁż┐źūźĒź░źķź▐żŽFPGAż╬└▀╝ŖżŌ▓─ē”ż╦ĪĪĮąųZĪ¦Altera

żĄżķż╦╣ŌĮĖ└čż╩źóźūźĒĪ╝ź┴ż╦żŽOpenCLż“Ų│Ų■ż╣żļĪŻż│żņżŽĪóCĖ└Ėņż“ź┘Ī╝ź╣ż╦żĘż┐źūźĒź░źķź▀ź¾ź░Š}╦ĪżŪĪó╩┬š`▒ķōQż╬ź▐źļź┴CPUź│źóżõĪóGPUżõDSPż╬ź│źóż¼Č”┘Tż╣żļźžźŲźĒźĖź╦źóź╣ż╩ź│źóż╩ż╔ż“ŠW(w©Żng)├ōżĘż┐╩┬š`ĮĶ═²ź│ź¾źįźÕĪ╝ź┐ż╦Ė■ż»ź─Ī╝źļżŪżóżļĪŻ╣ŌĮĖ└čż╬FPGAż╬źūźĒź░źķź▀ź¾ź░ż╦OpenCLż“╗╚ż├żŲżżż»ĪŻØŖż╦Ī󟻟ķź”ź╔ĖĪ║„ż╬źóź»ź╗źķźņĪ╝ź┐ż“AlterażŽ├µ╣±ż╬ĖĪ║„źĄźżź╚Īó╝å┼┘Ī╩BaiduĪ╦ż╚Č”Ų▒│½╚»żĘżŲżżżļĪŻĖĪ║„ż╚żżż”»éż▐ż├ż┐╝ŖōQż╦FPGAżŪ╝┬╣įż╣żļż╚╣ŌÅ]ż╦ż╩żļżąż½żĻżŪżŽż╩ż»ĪóCPUżõGPUż╬╔ķ▓┘ż“žō(f©┤)żķż╣ż│ż╚żŌżŪżŁżļĪŻż│żņż▐żŪCPUż╩ż╔ż╬źĮźšź╚ź”ź©źó│½╚»ż╦Ę╚ż’ż├żŲżŁż┐CĖ└ĖņźūźĒź░źķź▐żŽĪó║ŻĖÕOpenCLżŪźŽĪ╝ź╔ź”ź©źó└▀╝ŖżŌżŪżŁżļżĶż”ż╦ż╩żļ(┐▐2)ĪŻ

Ų╚śOż╬ź»źķź”ź╔╝ŖōQĄĪż“Ęeż─Synapse

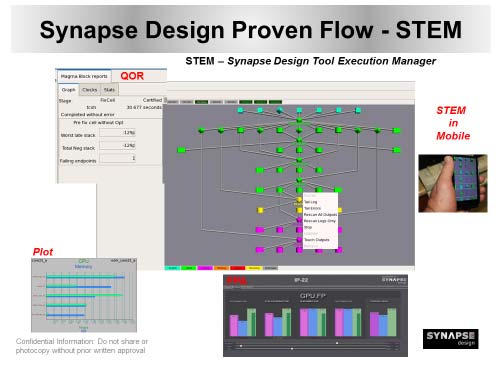

źŪźĖź┐źļżŌźóź╩źĒź░żŌ└▀╝ŖżŪżŁżļźŪźČźżź¾źŽź”ź╣ż╬Synapse DesignżŽĪóRTLż╦▓├ż©ĪóVerlog-Aż╚SPICEż“Ęeż├żŲż¬żĻĪóźšźĪĪ╝ź╣ź╚źĘźĻź│ź¾żŪ┤░µ£Ų░║Ņ▓─ē”ż╩ź┴ź├źūż“─¾ČĪż╣żļż│ż╚ż“ØŖ─╣ż╚żĘżŲżżżļĪŻŲ╚śO│½╚»żĘż┐EDAź─Ī╝źļż╬STEMĪ╩Synapse Design Tool Execution ManagerĪ╦ż“├ōżżĪ╩┐▐3Ī╦Īó┘ćżĘżż└▀╝ŖźšźĒĪ╝ż“┤╔═²żĘżŲżżżļĪŻ║ŪŖZż╬12ź§ĘŅżŪ33¹|╬ÓSoCż“└▀╝ŖżĘż┐ż╚żżż”ĪŻż│ż╬SoCż╦żŽ14nm FinFETżõ28nm FD-SOIż╦▓├ż©Īó28nmHPM/HPL/SLPż╩ż╔ż╬║Ū└Ķ├╝ż╬źšźĪź”ź¾ź╔źĻźūźĒź╗ź╣żŌ┤▐ż¾żŪżżżļĪŻµ£żŲ500mm2░╩æųż╬ź┴ź├źūźĄźżź║żŪĪóźšźĪĪ╝ź╣ź╚źĘźĻź│ź¾żŪŲ░║ŅżĘż┐ż╚żĘżŲżżżļĪŻ

┐▐3ĪĪSynapseż╬└▀╝Ŗ┤╔═²ź─Ī╝źļSTEMĪĪĮąųZĪ¦Synapse Design

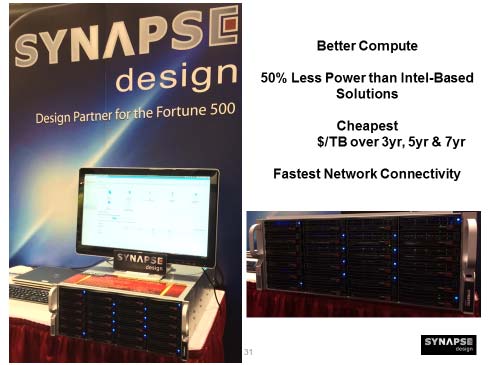

Ų▒╝꿎Īó└▀╝ŖÄźĖĪŠ┌ż╦┤žż╣żļ▒ķōQż“╣ŌÅ]ż╦ż╣żļż┐żßĪó└ņ├ōż╬ź│ź¾źįźÕĪ╝ź┐(źūźķź├ź╚źšź®Ī╝źÓ)ż“ź»źķź”ź╔└▀╝Ŗ├ōż╦║Ņż├ż┐ĪŻIntelż╬źūźĒź╗ź├źĄż“╗╚ż’ż║ż╦Freescależ╬T4240ź═ź├ź╚ź’Ī╝ź»źūźĒź╗ź├źĄż“CPUż╚żĘżŲ╗╚żżĪóŠ├õJ┼┼╬üż“╚Šžō(f©┤)żĄż╗ż┐ż╚żĘżŲżżżļĪŻ├ōżżż┐OSżŽĪóź¬Ī╝źūź¾źĮĪ╝ź╣ż╬ź»źķź”ź╔OSżŪżóżļOpenStackż╬║Ū┐Ę╚ŪIcehouseżŪżóżļĪŻSoC└▀╝Ŗż“Īóż│ż╬ź»źķź”ź╔ź│ź¾źįźÕĪ╝ź┐żŪ╝┬╣įż╣żļĪŻż│ż╬źūźķź├ź╚źšź®Ī╝źÓżŽĪó24Ė─ż╬źūźĒź╗ź├źĘź¾ź░ź╣źņź├ź╔Īó4ź┴źŃź¾ź═źļż╬10Gb EthernetĪó8ź┴źŃź¾ź═źļż╬1Gb EthernetĪó96TBż╬SSDż“Ęeż─ż¼Īóż│ż╬╣Į└«ż“Įj(lu©░)żŁż»╩čż©żķżņżļź│ź¾źšźŻź«źÕźóźķźųźļż╩źŽĪ╝ź╔ź”ź©źóżŪżŌżóżļż╚żżż”ĪŻźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╬Š├õJ┼┼╬üż“žō(f©┤)żķżĘż╩ż¼żķĪó▒ķōQÅ]┼┘ż“æųż▓ż┐ż┐żßTCOĪ╩total cost of ownershipĪ╦żŌ║’žō(f©┤)żŪżŁżļż╚żżż”ĪŻ

┐▐4ĪĪ│½╚»żĘż┐ź»źķź”ź╔└▀╝Ŗ├ō└ņ├ōź│ź¾źįźÕĪ╝ź┐ĪĪĮąųZĪ¦Synapse Design

╗▓╣═½@╬┴

1. ╣ŌĮĖ└迎└▀╝ŖČ\ĮčżŌ║żžMż╦Ī¦└▀╝Ŗź─Ī╝źļįćĪ┴EuroAsia(2) (2014/10/17)