EB─ŠķWż╬eASICż¼Tensilicaż╬źūźĒź╗ź├źĄź│źóżŪSoCżž┐╩Įą

1┴žż╬źėźóŪ█└■ż╬ź▐ź╣ź»źčź┐Ī╝ź¾ż└ż▒ż“┼┼╗ęźėĪ╝źÓż╬─Š└▄ķW▓Ķż╦żĶżĻź▐ź╣ź»źņź╣żŪźčź┐Ī╝ź¾ż“ķWż»ż│ż╚ż“ØŖ─╣ż╚żĘżŲżŁż┐ä▌╣±źšźĪźųźņź╣eASIC╝ęż╬ø]Ū╝┤³└Łż╚ĪóTensilica╝ęDiamondźšźĪź▀źĻż╬ź│źóż╬Š«żĄż╩ĀC└čż“ØŖ─╣ż╚ż╣żļ32źėź├ź╚źūźĒź╗ź├źĄż“┴╚ż▀╣ńż’ż╗żļż│ż╚żŪĪó┴╚ż▀╣■ż▀źĘź╣źŲźÓ└▀╝ŖŪvżŽDiamondź┘Ī╝ź╣ż╬SoCż“ż’ż║ż½4ĮĄ┤ųżŪ×æļ]żŪżŁżļżĶż”ż╦ż╩żļĪŻ

ä▌╣±źšźĪźųźņź╣ż╬ź╣ź╚źķź»ź┴źŃĪ╝ź╔ASICźßĪ╝ź½Ī╝żŪżóżļeASIC╝꿎ĪóźūźĒź╗ź├źĄIPź┘ź¾ź└Ī╝żŪżóżļTensilica╝ęż╚źčĪ╝ź╚ź╩Ī╝źĘź├źūż“±TżėĪóTensilica╝ęż╬║YØŹ┼¬ż╩źūźĒź╗ź├źĄżŪżóżļDiamondźšźĪź▀źĻż╬ź│źóż“┴╚ż▀╣■żÓż│ż╚żŪĪóø]Ū╝┤³ż╬┴╚ż▀╣■ż▀ź┴ź├źūż“─¾ČĪżŪżŁżļżĶż”ż╦ż╩żļĪóż╚╚»╔ĮżĘż┐ĪŻŻ▒┴žż╬źėźóŪ█└■ż╬ź▐ź╣ź»źčź┐Ī╝ź¾ż└ż▒ż“┼┼╗ęźėĪ╝źÓż╬─Š└▄ķW▓Ķż╦żĶżĻź▐ź╣ź»źņź╣żŪźčź┐Ī╝ź¾ż“ķWż»ż│ż╚ż“ØŖ─╣ż╚żĘżŲżŁż┐eASIC╝ęż╬ø]Ū╝┤³└Łż╚ĪóTensilica╝ęż╬Š«żĄż╩ĀC└čż“ØŖ─╣ż╚ż╣żļ32źėź├ź╚źūźĒź╗ź├źĄż“┴╚ż▀╣ńż’ż╗żļż│ż╚żŪĪó┴╚ż▀╣■ż▀źĘź╣źŲźÓ└▀╝ŖŪvżŽDiamondź┘Ī╝ź╣ż╬SoCż“ż’ż║ż½4ĮĄ┤ųżŪ×æļ]żŪżŁżļżĶż”ż╦ż╩żļĪŻ

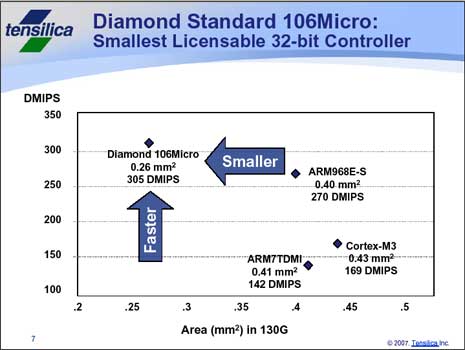

ź│ź¾źšźŻź«źÕźķźųźļĪ”źūźĒź╗ź├źĄż╬Xtensaż¼Ń~ć@ż╩Tensilica╝ężŪżóżļż¼Īó║Żöv─¾Ę╚żĘż┐ż╬żŽĪóź│ź¾źšźŻź«źÕźķźųźļżŪżŽż╩żżźūźĒź╗ź├źĄź│źóżŪĪóĀC└čż╬Š«żĄżĄż“ŪõżĻرż╦żĘżŲżżżļĪŻ130nm└ż┬Õż╬źūźĒź╗ź╣żŪ╚µ│ėż╣żļż╚DiamondźĘźĻĪ╝ź║ż╬├µżŪżŽ║ŪŠ«ĀC└čż╬305DMIPSż╬32źėź├ź╚Ī”źŁźŃźĘźÕźņź╣RISCżŪżóżļ106Microź│źóż╬ĀC└迎ż’ż║ż½0.26╩┐öĄmmżĘż½ż╩żżĪŻ

eASIC╝ęż¼źķźżźąźļż╚Ė½żļFPGAźŪźąźżź╣ż“ĪóŲ▒żĖźóźļź┤źĻź║źÓż╚Ų▒żĖźūźĒź╗ź╣ż╬Š“°PżŪ╚µż┘żļż╚Īóź┴ź├źūĀC└迎1/4µć┼┘ż╦ż╩żĻĪóŠ├õJ┼┼╬üżŽ1/10░╩▓╝ż╦ż╩żļż╚żżż”ĪŻ╬ŠŪvż╬╚»╔ĮżŪżŽĪóźėźŪź¬┤Ų£åź½źßźķżž▒■├ōżĘż┐Šņ╣ńż╬źŪźŌż“╣įżżĪóFPGAż╦żĶżļźĘź╣źŲźÓżŪżŽ1.2VżŪ4.9Aż╬┼┼╬«ż“Š├õJżĘż┐ż¼ĪóeASIC╝ęż╬źŪźąźżź╣żŪżŽ1.2VżŪ0.28AżĘż½Š├õJżĘż╩ż½ż├ż┐ĪŻ

eASIC╝ęż╬ź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷źĘź╦źóźŪźŻźņź»ź┐żŪżóżļJasbinder BhootĢ■ż╦żĶżļż╚ĪóĪųż│żņż▐żŪż╬ź╣ź╚źķź»ź┴źŃĪ╝ź╔ASICżŽź½ź╣ź┐źÓŪ█└■ż¼┐¶┴žż╦żŌż’ż┐żĻĪó╚∙║┘▓Įż¼┐╩żÓ╗■┬Õż╦żŽ└▀╝Ŗż¼žMżĘż»ż╩żĻĪóEDAźßĪ╝ź½Ī╝ż╬ź─Ī╝źļż╬─┤┼DżŌØŁ═ūż╦ż╩ż├żŲżżż┐ĪŻż│ż╬ż┐żßĪóź╣ź╚źķź»ź┴źŃĪ╝ź╔ASICżŽż╣ż┐żņżŲżŁż┐ż¼ĪóeASIC╝ęż╬Š}╦ĪżŽźėźó┴ž1┴žż└ż▒ż“┼┼╗ęźėĪ╝źÓ─ŠķWżŪź½ź╣ź┐źÓŪ█└■ż╣żļŲ╚śOż╬öĄ╦Īż╩ż╬żŪEDAź─Ī╝źļż╦żĶżļDFMż“ŲDżĻŲ■żņżļØŁ═ūż¼ż╩ż»Īóį~├▒ż╦└▀╝ŖżŪżŁżļĪūż╚żĘżŲżżżļĪŻ┼┼╗ęźėĪ╝źÓż╬─ŠķWżŽ╔┘╗╬─╠ż╦░══ĻżĘżŲżżżļĪŻ

eASICż¼║ŪĮķż½żķļmżß╣■ż¾żŪżżżļżĄż▐żČż▐ż╩IPź│źóżŽż╣ż┘żŲĖĪŠ┌║čż▀żŪĪóźĘź░ź╩źļźżź¾źŲź░źĻźŲźŻż╬ź┴ź¦ź├ź»ż╩ż╔żŽ╔į═ūż└ż╚żżż”ĪŻ╗╚ż©żļTensilicaż╬źūźĒź╗ź├źĄź│źóżŽ106Micro░╩│░żŪżŽĪó░╩▓╝IPż¼żóżļĪ©

108MiniĪ¦DSPĄĪē”ż“║ŅżĻ¤²ż▒żŪĘeż┴ż╩ż¼żķźŁźŃź├źĘźÕźņź╣ż╬32źėź├ź╚RISCź│ź¾ź╚źĒĪ╝źķź│źó

211GPĪ¦ź▀ź├ź╔źņź¾źĖż╬32źėź├ź╚RISCź│ź¾ź╚źĒĪ╝źķź│źó

232LĪ¦LinuxOSż“źĄź▌Ī╝ź╚ż╣żļż┐żßMMUĪ╩źßźŌźĻ┤╔═²źµź╦ź├ź╚Ī╦ż“┼ļ║▄ż╣żļź▀ź├ź╔źņź¾źĖż╬32źėź├ź╚CPUź│źó

570TĪ¦źŽźżź©ź¾ź╔ż╬32źėź├ź╚CPUź│źó

545CKĪ¦╣Ō└Łē”ż╬DSPź│źó

330HiFiĪ¦ź¬Ī╝źŪźŻź¬ż¬żĶżė▓╗╠mź│Ī╝źŪź├ź»ż“źĄź▌Ī╝ź╚żĘżŲżżżļ─ŃŠ├õJ┼┼╬üż╬24źėź├ź╚DSPźūźĒź╗ź├źĄ

ż│żņżķżŽDiamondż╬║YØŹ┼¬ż╩źĮźšź╚ź”ź©źóź─Ī╝źļż“╗╚ż©ĪóTensilicaż╬Ęeż─Č╚─cż╬Č©╬ü┤žĘĖż¼┘Jż╦╣Į├█żĄżņżŲżżżļż┐żßĪó└▀╝Ŗż╬ź©ź│źĘź╣źŲźÓż¼żŪżŁżŲżżżļĪŻ

Diamondż¼Š»ż╩żżĀC└čżŪźūźĒź╗ź├źĄĄĪē”ż“ĘeżŲżļż╬żŽĪóżĶż»╗╚ż”16źėź├ź╚ż¬żĶżė24źėź├ź╚ż╬╠┐╬ßź╗ź├ź╚ż└ż▒ż╦╣╩żĻĪóź│Ī╝ź╔Ė·╬©ż“æųż▓ż┐ż┐żßż└ż╚Tensilica╝ęź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷źąźżź╣źūźņźĖźŪź¾ź╚ż╬Steve RoddyĢ■żŽ└Ō£½żĘżŲżżżļĪŻ

┤žŽóĄŁĄ£Ī¦

Ī”65nm░╩▓╝ż╬EB─ŠķWż╦┼ęż▒żļźżĪ╝Ī”źĘźŃź╚źļĪĪ2007ŃQ10ĘŅ 9Ų³

Ī”Xilinxż¼32źėź├ź╚źūźĒź╗ź├źĄż╬│½╚»źĘź╣źŲźÓż“IPż▐żŪ┤▐żßżŲ▐k╝░źĄź▌Ī╝ź╚ĪĪ2007ŃQ11ĘŅ26Ų³

Ī”ź▐źļź┴ź│źóżĶżĻź▐źļź┴ź╣źņź├ź╔żŪ└Łē”ż“æųż▓ż╩ż¼żķźĘźĻź│ź¾ĀC└čż“║’žōĪĪ2007ŃQ11ĘŅ 8Ų³