28nmż╬╝Īż╬źūźĒź╗ź╣ź╬Ī╝ź╔żŽĪó14nm FINFETż½20nmźūźņĪ╝ź╩ż½

Mooreż╬╦Īō¦ż╬źŲź»ź╬źĒźĖĪ╝ź╬Ī╝ź╔ż“ź╣źŁź├źūż╣żļŲ░żŁż¼Ė▓├°ż╦ż╩ż├żŲżŁż┐ĪŻAlterażŽĪ󟎟żź©ź¾ź╔ż╬FPGA SoC×æēäStratixĪóź▀ź├ź╔źņź¾źĖż╬Arria×æēäż“ĖĮ║▀║Ū└Ķ├╝ż╬28nmźūźĒź╗ź╣żŪÖ┌ŠÅżĘżŲżżżļż¼Īóż│ż╬╝Īż╬źūźĒź╗ź╣ź╬Ī╝ź╔ż“żĮżņżŠżņ14nm FINFETĪó20nmźūźņĪ╝ź╩CMOSż╚Īó╩čśŗż╣żļöĄ┐╦ż“╚»╔ĮżĘż┐ĪŻ×æēäć@żŽżżż║żņżŌ10źĘźĻĪ╝ź║ż╚╠┐ć@żĘżŲżżżļ(┐▐1)ĪŻ

┐▐1ĪĪAlteraż╬┐ĘSoC

UMCż¼└@├ōPDKĪ╩źūźĒź╗ź╣│½╚»źŁź├ź╚Ī╦ż“─¾ČĪż╣żļ×æļ]Č\Įčż╚żĘżŲĪó28nmż½żķ20nmż“ź╣źŁź├źūżĘżŲ14nm FINFETźūźĒź╗ź╣żž╚¶żųż│ż╚ż“ż╣żŪż╦╚»╔ĮżĘżŲżżżļ(╗▓╣═½@╬┴1)ĪŻ║Żövż╬Alteraż╬źŽźżź©ź¾ź╔×æēäStratixżŌ28nmż½żķ14nm FINFETżž╚¶żųĪŻż│ż╬14nm FINFETźūźĒź╗ź╣żŽĪóIntelż¼×æļ]ż╣żļż¼Ī╩╗▓╣═½@╬┴2Ī╦Īó┘ć│╬ż╦żŽ└@├ōż╬źšźĪź”ź¾ź╔źĻżŪżŽż╩ż»ĪóIntelż╚ż╬Ų╚žéĘ└╠¾ż╬×æļ]░č▓mĪ╩exclusive partnershipĪ╦ż╦ż╩żļĪóż╚Altera×æēäź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷źĘź╦źóźŪźŻźņź»ź┐ż╬Patrick DorseyĢ■żŽĮęż┘żŲżżżļĪŻ

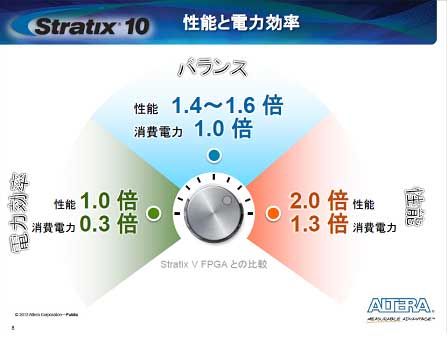

14nm FINFETźūźĒź╗ź╣ż“╗╚ż”Stratix 10ż╬└Łē”żŽĪó28nmż╬Øi└ż┬ÕStratix 5żŪżŽź»źĒź├ź»╝■āS┐¶ż¼║ŪĮj500MHzż└ż├ż┐ż¼Īó14nm FINFETźūźĒź╗ź╣ż╬źĘź▀źÕźņĪ╝źĘźńź¾żŪżŽ2Ū▄ż╬1GHzż“┐āżĘż┐ż╚żżż”ĪŻż│ż╬╗■ż╬Š├õJ┼┼╬üżŽ1.3Ū▄ż╦╣Ōż»ż╩ż├ż┐ĪŻ└Łē”ż“Stratix 5ż╚Ų▒żĖ500MHzż╦└▀─Ļż╣żļż╚Š├õJ┼┼╬üżŽ0.3Ū▄ż╚ż╩żĻĪóŠ├õJ┼┼╬üż“Øi└ż┬Õż╚Ų▒żĖż╦└▀─Ļż╣żļż╚└Łē”żŽ1.4Ī┴1.6Ū▄ż╦Ė■æųż╣żļ(┐▐2)ĪŻ

┐▐2ĪĪ└Łē”Ī”Š├õJ┼┼╬üż“Øi└ż┬ÕStratix 5ż╚╚µ│ėż╣żļĪĪĮąųZĪ¦Altera

Stratix 10ż╦żŽĪóCPUź│źóż╦▓├ż©ĪóDSPź│źóĪóFPGAźĒźĖź├ź»ź©źņźßź¾ź╚ż╩ż╔ż“ĮĖ└čżĘżŲżżżļĪŻFPGAŗ╩¼ż“Ų■Įą╬üż╬ź╚źķź¾źĘĪ╝źąövŽ®ż╚żĘżŲ╗╚ż”ż│ż╚ż¼¾Hżżż¼ĪóŲ¾─_┴„£p┐«ż╬└Łē”ż╚żĘżŲ56Gbpsż╬└Łē”ż“įużŲżżżļĪŻFPGAŗ╩¼żŽØi└ż┬Õż╬4Ū▄ż╬400╦³źĒźĖź├ź»ź©źņźßź¾ź╚ż╬ĮĖ└č┼┘ż“Ęeż─ĪŻDSPżŽĪó├▒╗@┼┘ż╬Šņ╣ńż╦10 TFLOPSż╚Øi└ż┬Õż╬10Ū▄ż╬╔ŌŲ░Š«┐¶┼└▒ķōQ└Łē”ż“įużŲżżżļĪŻ

ż▐ż┐ĪóSRAMżõDRAMż“▐kż─ż╬źčź├ź▒Ī╝źĖŲŌż╦2.5╝ĪĖĄżóżļżżżŽ3╝ĪĖĄżŪ╝┬äóż╣żļČ\ĮčżŌØŹ×óżĘżŲżżżļż╚żżż”ĪŻżżż’żąź’źżź╔I/Oż╬źßźŌźĻż╦żĶż├żŲĪóźĒźĖź├ź»Ī╩Stratix 10Ī╦ż╚╣ŌÅ]ż╦żõżĻŲDżĻż╣żļż│ż╚żŪźĘź╣źŲźÓĮĶ═²Å]┼┘ż“Ė■æųżĄż╗żĶż”ż╚żżż”Š}╦Īż└ĪŻ

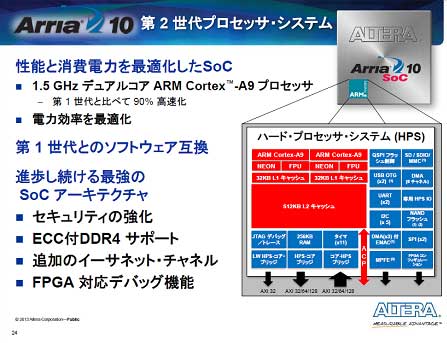

Arria 10źĘźĻĪ╝ź║żŌStratix 10ż╚Ų▒══ĪóźšźļFPGA╚ŠŲ│öüżŪżŽż╩ż»ĪóCPUź│źóżõźŁźŃź├źĘźÕźßźŌźĻĪó╔ŌŲ░Š«┐¶┼└źµź╦ź├ź╚övŽ®ż╩ż╔ż╦FPGAż“ĮĖ└čżĘż┐SoCżŪżóżļĪ╩┐▐3Ī╦ĪŻż┐ż└żĘĪ󿥿▐żČż▐ż╩źżź¾ź┐Ī╝źšź¦Ī╝ź╣övŽ®ż“ĮĖ└čżĘĪóźūźĒź░źķź▐źųźļż╩FPGAövŽ®żŽŠ»ż╩żżĪŻ▒ķōQ├ōCPUż╦żŽźŪźÕźóźļź│źóż╬ARM Cortex-A9 MP coreż“ĮĖ└čĪó1.5GHzżŪŲ░║Ņż╣żļĪŻTSMCż╬20nmLPźūźĒź╗ź╣ż“ŠW├ōż╣żļĪŻ└Łē”ż╚─ŃŠ├õJ┼┼╬üż“Ę¾ż═×óż©ż┐║Ū╬╔ż╬źūźĒź╗ź╣ż└ż╚DorseyĢ■żŽĖ└ż”ĪŻ

┐▐3ĪĪArria 10ĪóFPGAż╚żżż”żĶżĻżŽSoCĪĪĮąųZĪ¦Altera

żżż║żņż╬FPGAżóżļżżżŽSoCż╦ż─żżżŲżŌAlterażŽ│½╚»ź─Ī╝źļż“├ō┴TżĘżŲżżżļĪŻźŽĪ╝ź╔ź”ź©źó└▀╝ŖŪvż╦żŽĪóź│ź¾źčźżźļ╗■┤ųż“1/8ż╦ø]Į╠żŪżŁżļQuartus IIĪóMathWorksż╬SimuLinkż╬źŌźŪźļź┘Ī╝ź╣└▀╝Ŗż╚źĘź▀źÕźņĪ╝źĘźńź¾ż“ŠW├ōż╣żļDSP DesignerĪóźĮźšź╚ź”ź©źó│½╚»Ūvż╦żŽĪóAltera SDK for OpenCLż“─¾ČĪż╣żļĪŻż│żņż╦żĶżĻ└▀╝Ŗż╬Ö┌ŠÅ└Łż¼Ė■æųż╣żļĪŻ

╗▓╣═½@╬┴

1. ±śŽčUMCĪó20nmż“ź╣źŁź├źūĪó14nmFINFETźūźĒź╗ź╣żŪ┤¼żŁ╩ųżĘ┴└ż” (2013/05/30)

2. AlteraĪó14nmż╬IntelźšźĪź”ź¾ź╔źĻĪó55nmźšźķź├źĘźÕĪóźĒĪ╝ź╔ź▐ź├źūż“Ėņżļ (2013/05/02)