TSMCż¼╩č┐╚ż½Īó10ŃQżųżĻż╬ĄŁŪv▓±Ė½żŪźĒĪ╝ź╔ź▐ź├źū┐āż╣

TSMCż¼10ŃQżųżĻż╦Ų³╦▄żŪĄŁŪv▓±Ė½ż“│½żżż┐ĪŻŲ▒╝꿎╦ĶŃQTSMC Technology Symposiumż“└ż─cĘQ├ŽżŪ│½╠¢żĘżŲż¬żĻĪóä▌╣±żõ±śŽčż╬źßźŪźŻźóżŽ╗▓▓├żŪżŁż┐ż¼Ų³╦▄ż╬źĘź¾ź▌źĖź”źÓżŽźßźŪźŻźóż“─∙żßĮążĘĄŁŪv▓±Ė½żĄż©│½╠¢żĘżŲż│ż╩ż½ż├ż┐ĪŻTSMCż╬ĖĮėXż“źņź▌Ī╝ź╚ż╣żļĪŻ

┐▐1ĪĪTSMC╝ęCorporate Communicationsŗ╠ńźĘź╦źóźŪźŻźņź»ź┐ż╬Elizabeth SunĢ■

ż│żņż▐żŪż╬TSMCż╦żŽĪóĪųą■╦²ż╦ż╩ż├ż┐ĪūĪóĪųź┘ź¾ź┴źŃĪ╝żŽ┴ĻŠ}ż╦żĘżŲżŌżķż©ż╩żżĪūż╚żżż├ż┐╠mż“╩╣żżż┐ĪŻżĘż½żĘĪó▓±Ė½żõźĘź¾ź▌źĖź”źÓż╦żŽ╗▓▓├żŪżŁż╩ż½ż├ż┐ż┐żßĪó╦▄┼÷ż╬ųeż“Ų³╦▄ż╬źßźŪźŻźóżŽ┬¬ż©żļż│ż╚ż¼żŪżŁż╩ż½ż├ż┐ĪŻż┐ż└żĘĪóż│ż│┐¶ŃQTSMCżŽ╩čż’ż├ż┐Īóż╚żżż”╠mżŌ╩╣żżż┐ĪŻż╔ż”╩čż’ż├ż┐ż╬ż½ĪŻŲ▒╝ęCorporate Communicationsŗ╠ńźĘź╦źóźŪźŻźņź»ź┐ż╬Elizabeth SunĢ■(┐▐1)żŽĪóTSMCż╬įÆż─ż╬äėżĄż╚żĘżŲĪóĪųČ\ĮčźĻĪ╝ź└Ī╝ĪūĪóĪų┴R▒█żĘż┐×æļ]Č\ĮčĪūĪóĪųĖ▄Ąęż╬┐«═Ļż╬Ė³żĄĪūż“æųż▓ĪóĪųTSMCżŽ┐«═Ļż╬Ė³żżźĄźūźķźżźõĪ╝żŪż╣Īūż╚▓┐┼┘żŌĖņż├ż┐ĪŻĪųHonestyĪ╩┘ć─ŠĪ╦ż╚TrustĪ╩┐«═ĻĪ╦Īūż¼TSMCż╬┤ļČ╚╩Ė▓ĮżŪżóżĻĪó▐kĖ└żŪżżż©żąIntegrityĪ╩źŌźķźļżõĖ▄Ąęż╦├ķ╝┬Ī╦ż“32ŃQ┤ųÅ─żŁ─╠żĘżŲżŁż┐ż╚ĖžżļĪŻżóżļ╗■┤³ż╦╩╣żżż┐ĪųArrogantĪ╩ą■╦²ż╩Ī╦Īūż╩▌å┼┘ż“╚┐Š╩żĘż┐ż╬ż½żŌżĘżņż╩żżĪŻ

2019ŃQŗī1╗═╚Š┤³ż╦źšźĪź”ź¾ź╔źĻ┤ļČ╚ż¼Ė«╩┬ż▀2ź▒ź┐ż╬═Ņż┴╣■ż▀ż“┐āżĘż┐├µĪ╩╗▓╣═½@╬┴1Ī╦żŪĪó4%žōż╬═Ņż┴╣■ż▀żŪ║čż¾ż└TSMCżŽĪóĪų7nmźūźĒź╗ź╣ż¼╝²▒ūż╦╣ūĖźżĘż┐Īūż╚SunĢ■żŽĖņżļĪŻż│ż╬ŗī2╗═╚Š┤³ż╬Ė½─╠żĘż╦×┤żĘżŲżŌĪóŗī1╗═╚Š┤³ż¼71▓»ź╔źļż╬ŪõżĻæųż▓ż╦×┤żĘżŲĪó76▓»ź╔źļż╦ż╩żĻżĮż”ż╩Ė½╣■ż▀ż└ż╚Ėņż├żŲżżżļĪŻźūźĒź╗ź╣╩╠ż╬ŪõżĻæųż▓żŪżŽĪó7nmźūźĒź╗ź╣ż╬ŪõżĻæųż▓żŽŗī1╗═╚Š┤³ż╦żŽ22%ż└ż¼Īóŗī3╗═╚Š┤³ż▐żŪż╦30%ż╦├Żż╣żļż╬żŪżŽż╩żżż½ż╚ż▀żŲżżżļĪŻ2018ŃQŗī3╗═╚Š┤³ż╦ĮķżßżŲŪõżĻæųż▓ż¼╝ŖæųżĄżņż┐7nmźūźĒź╗ź╣żŽĪóżĮż╬╝²▒ū╬üż“ŠåÅ]ż╦╗\żĘżŲżżżļĪŻ2019ŃQż╬─╠ŃQżŪżŽµ£Ūõæųż╬25%ż╦ż╩żĻżĮż”ż└ż╚żĘżŲżżżļĪŻ

┐▐2ĪĪ└Ķ├╝ż╬7nmż½żķ0.5µmäėż▐żŪ┬Ęż©żŲżżżļTSMC

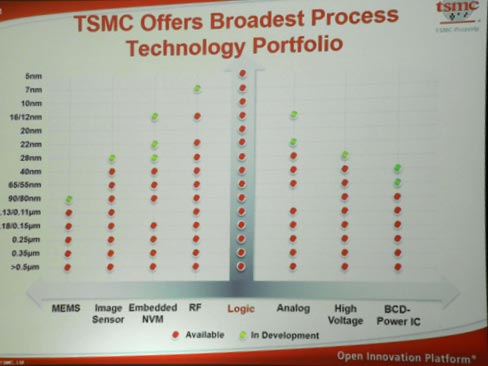

Ūõæų±Yż╬▌xŠņ╩╠żŪżŽĪóź╣ź▐Ī╝ź╚źšź®ź¾ż¼║ŪĮjż└ż¼Īóż│żņż½żķżŽHPCĪ╩╣Ō└Łē”ź│ź¾źįźÕĪ╝źŲźŻź¾ź░Ī¦żżż’żąźŪĪ╝ź┐ź╗ź¾ź┐Ė■ż▒ż╬źŽźżź©ź¾ź╔źĄĪ╝źąĪ╝żõź╣Ī╝źčĪ╝ź│ź¾źįźÕĪ╝ź┐ż╩ż╔Ī╦╩¼╠Ņż¼└«─╣ż╣żļż╚Ė½żŲżżżļĪŻź╣ź▐ź█żŪżŽĪóQualcommżõAppleĪóMediaTekĪóHiSiliconż╩ż╔ż¼źŌźŪźÓżõźóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄż╬×æļ]ż“TSMCż╦░══ĻżĘżŲżżżļż½żķż└ĪŻHPCżŪżŽNvidiażõXilinxż╩ż╔ż¼░══ĻżĘżŲż¬żĻĪó╚∙║┘▓ĮČ\ĮčżŪżŽ┬Šż╬źšźĪź”ź¾ź╔źĻż“źĻĪ╝ź╔żĘżŲżżżļĪŻżŌż┴żĒż¾Īó7nmż¼╝²▒ūż╦╣ūĖźżĘż┐ż╚żżż├żŲżŌĪóżĮżņ░╩│░ż╬źŪźČźżź¾źļĪ╝źļż╬źūźĒź╗ź╣żŌżĮżĒż©żŲżżżļ(┐▐2)ĪŻ

TSMCż¼║ŻövĪó▓±Ė½ż“│½żżż┐═²Įyż╬▐kż─ż“Īó║“ŃQSamsungż¼Ų³╦▄żŪżŌźšźĪź”ź¾ź╔źĻźėźĖź═ź╣ż“┐õ┐╩żĘżŲżżżļż│ż╚ż“┴╩ĄßżĘĪóźĘź¾ź▌źĖź”źÓż╚ĄŁŪv▓±Ė½ż“│½╠¢żĘ(╗▓╣═½@╬┴2)Ī󿥿▐żČż▐ż╩źßźŪźŻźóż¼╩¾żĖż┐ż│ż╚żŌ║Żövż╬│½╠¢ż╬═ū░°ż╬▐kż─ż╚ż▀żļĖ■żŁżŌżóżļĪŻSamsungż¼7nmźūźĒź╗ź╣░╩æT3nmż▐żŪż╬źĒĪ╝ź╔ź▐ź├źūż“┐āżĘż┐ż╬ż╦×┤żĘĪó║ŻövTSMCżŽ5nmż▐żŪż╬▌Ś╝┬ż╩źĒĪ╝ź╔ź▐ź├źūż“ķWżżż┐ĪŻ

ż│żņż▐żŪ7nmźūźĒź╗ź╣ż╬▒■├ōżŽĪóHPCżõ▓Š„[─╠▓▀ż╬░┼ęÄ▓“Ų╔ź┴ź├źūż└ż├ż┐ż¼Īó▓Š„[─╠▓▀ż¼║“ŃQĖÕ╚Šż╦Šå═ŅżĘĪóżĘżążķż»żĮż╬▓┴│╩żŽ─Ń╠┬ż“¶öż▒żŲżżż┐ĪŻ║ŪŖZĪó║Ųżė▓Š„[─╠▓▀▓┴│╩żŽæųż¼żĻ╗ŽżßżŲżżżļĪŻĪųź╣ź▐ź█ż╦żŌ┤ųżŌż╩ż»7nmż“╗╚ż├ż┐×æēäż¼ĮążŲż»żļĪūż╚Ų▒╝ęBusiness Development├┤┼÷VPż╬Kevin ZhangĢ■(┐▐3)żŽĖņżļĪŻ7nmż╚żżż├ż┐╚∙║┘▓ĮżŽźŌźŪźÓżõźóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄĪóFPGAż╩ż╔ż“┤▐żÓźĒźĖź├ź»ź┴ź├źūż¼▓├Å]żĄż╗żŲżżż»ĪŻ

┐▐3ĪĪTSMC╝ęBusiness Development├┤┼÷VPż╬Kevin ZhangĢ■

TSMCż╬╚∙║┘▓ĮźĒĪ╝ź╔ź▐ź├źūżŽĪó7nmźūźĒź╗ź╣░╩æTżŪżŽż│żņż▐żŪż╚żŽ░ŃżżĪ󿵿├ż»żĻż╚żĘż┐ź┌Ī╝ź╣żŪ╩ŌżÓĪŻż│żņż▐żŪżŽĪó28nmż╬╝Īż¼20nmżóżļżżżŽ14/16nmĪ󿥿ķż╦10nmĪóżĮżĘżŲ7nmż╚żõż├żŲżŁż┐ĪŻż╚ż│żĒż¼Īó7nm░╩æTżŽżŌż├ż╚żµż├ż»żĻ╣’ż¾żŪżżż»ĪŻ

7nmźūźĒź╗ź╣ż“N7źūźĒź╗ź╣ż╚╔ĮĖĮżĘĪ󿥿ķż╦N7źūźĒź╗ź╣ż╬╝ĪżŽN7+źūźĒź╗ź╣ż╦ż╩żļż╚żżż”ĪŻN7źūźĒź╗ź╣ż╚ż╬░ŃżżżŽĪó7nmż“ź┘Ī╝ź╣ż╦żĘż╩ż¼żķ20%źĒźĖź├ź»╠®┼┘ż“æųż▓ż┐żŌż╬ż└ż╚żĘżŲżżżļĪŻż│ż╬N7+żŽEUVż“╬╠ŠÅżŪ╗╚ż”ĮķżßżŲż╬źūźĒź╗ź╣ż╚ż╩żļĪŻEUVČ\Įčż╬źóź┘źżźķźėźĻźŲźŻĪ╩▓─├ō└ŁĪ¦╗╚ż©żļėX▌åż“░▌ĘeżĘżŲżżżļ│õ╣ńĪ╦ż¼æųż¼żĻĪóÖ┌ŠÅ└Łż¼æųż¼żļż│ż╚ż“╝┬Š┌żĘżŲżŁż┐ĪŻźóź┘źżźķźėźĻźŲźŻżŽ2018ŃQż╬70%ż½żķ85%żžż╚æųż¼żĻĪó2020ŃQż╦żŽ90%░╩æųż╦ż╩żļĖ½╣■ż▀ż└ĪŻż▐ż┐ĪóEUVż╬Įą╬üżŽ280Wż“ŖW─ĻżĘżŲįużķżņżļżĶż”ż╦ż╩ż├żŲż¬żĻĪó2019ŃQż╦300WĪó2020ŃQż╦żŽ350Wż╦╣įżŁżĮż”ż└ż╚żżż”ĪŻN7+źūźĒź╗ź╣ż╬╬╠ŠÅżŽ2019ŃQĖÕ╚Šż½żķż╚żĘżŲżżżļĪŻ

żĮż╬╝ĪżŽN6źūźĒź╗ź╣żŪĪó7nmźūźĒź╗ź╣ż“ź┘Ī╝ź╣ż╦żĘżŲź╣ź▒Ī╝źĻź¾ź░żĘż┐żŌż╬ż└ż╚żżż”ĪŻ└Łē”żŽæųż¼żĻź│ź╣ź╚┼¬ż╦żŽŃ~ŠWż╦ż╩żĻżĮż”ż└ż╚żżż”ĪŻźŪźČźżź¾źļĪ╝źļżõSPICEźŌźŪźļĪóIPż╩ż╔żŽN7ż╚Ė▀┤╣└Łż¼żóżĻĪóEDAź─Ī╝źļżŌN7ż╚Ų▒żĖżŌż╬ż¼╗╚ż©żļĪŻ╣ŁżżšJ░Žż╬▒■├ōż“ų`╗žżĘźĻź╣ź»Ö┌ŠÅżŽ2020ŃQŗī1╗═╚Š┤³ż“═Į─ĻżĘżŲżżżļĪŻ

żĄżķż╦żĮż╬└Ķż¼N5źūźĒź╗ź╣ż└ĪŻźßźżź¾ż╬źĒźĖź├ź»ż“ź╣ź▒Ī╝źĻź¾ź░żĘż┐żŌż╬żŪĪó└Łē”żŽ15%æųż¼żĻĪóŠ├õJ┼┼╬üżŽ30%žōŠ»ĪóźĒźĖź├ź»╠®┼┘żŽ1.8Ū▄ż╦ż╩żļż╚żĘżŲżżżļĪŻż│ż│żŪżŽEUVźĻźĮź░źķźšźŻż“╗╚ż”źņźżźõĪ╝ż╬┐¶ż¼╗\ż©żļż╚żżż”ĪŻN7ż╚żŽ░Ńż”eLVTČ\Įčż“Ų│Ų■ż╣żļż╚żĘżŲżżżļĪŻż│żņżŽČ╦├╝ż╦─ŃżżżĘżŁżż┼┼░ĄVTČ\Įčż“┴T╠ŻżĘżŲżżżļĪŻźĻź╣ź»Ö┌ŠÅżŽ2019ŃQ3ĘŅż╦╗Žż▐ż├żŲżżżļĪŻ

żĮż╬└Ķż╦żŽN5PźūźĒź╗ź╣ż¼═ĶżļĪŻPżŽ+(źūźķź╣)ż╬┴T╠ŻĪŻż│żņżŽN5ż╚Ų▒żĖźŪźČźżź¾źļĪ╝źļż“╗╚żżż╩ż¼żķĪóżĘżŁżż┼┼░Ąż“▓╝ż▓żļż│ż╚ż╦żĶż├żŲ└Łē”ż“æųż▓żļČ\Įčż└ĪŻź╣źįĪ╝ź╔ż¼Ų▒żĖż╩żķŠ├õJ┼┼╬üżŽ▓╝ż¼żļČ\ĮčżŪżóżļĪŻ

┐▐4ĪĪ╣Ō┬č░ĄźŪźąźżź╣żõRFĪóźóź╩źĒź░Īóź╗ź¾źĄĪóNVMż╩ż╔ż“ĮĖ└čż╣żļź╣ź┌źĘźŃźļźŲźŻČ\Įčźūźķź├ź╚źšź®Ī╝źÓ

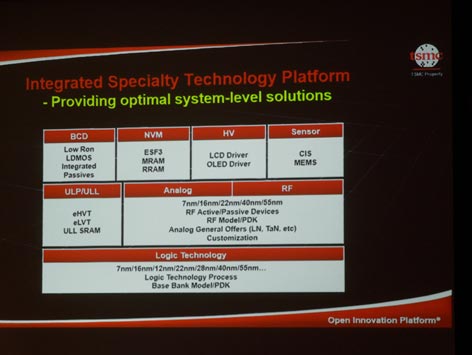

TSMCż¼─¾ČĪż╣żļźšźĪź”ź¾ź╔źĻČ\Įčż╦żŽĪó╣Ō┬č░Ąź╚źķź¾źĖź╣ź┐żõ╔įĦ╚»└ŁźßźŌźĻĪóź╗ź¾źĄż╩ż╔ż“ĮĖ└čż╣żļź╣ź┌źĘźŃźļźŲźŻČ\ĮčżŌżóżļ(┐▐4)ĪŻż│ż╬├µżŪØŖż╦Īó«Ć─ŃŠ├õJ┼┼╬«źūźĒź╗ź╣źūźķź├ź╚źšź®Ī╝źÓż╚żżż”Ę┴żŪĪóSRAMżõĪóRFż╚źóź╩źĒź░Īó┴╚ż▀╣■ż▀NVMĪ╩MRAMż╚ReRAMĪ╦ż“IoTżõAIż“╗╚ż├ż┐ź╣ź▐Ī╝ź╚╝ę▓±Ė■ż▒ź┴ź├źūż╚░╠Åø¤²ż▒żŲżżżļĪŻ

┴╚ż▀╣■ż▀├ō╔įĦ╚»└ŁźßźŌźĻ(eNVM)ż╚żĘżŲ°BŃ^╩č▓ĮĘ┐źßźŌźĻĪ╩RRAMĪ╦ż╚╝¦ĄżźßźŌźĻĪ╩MRAMĪ╦ż“├ō┴TżĘż┐ż╬żŽĪóźµĪ╝źČĪ╝ż½żķż╬═ū╦Šż╦żĶżļż╚ZhangĢ■żŽĖ└ż”ĪŻżĘż½żŌMRAMżŽ╝å╦³öv░╩æųż╬R/WĪ╩Ų╔ż▀ĮążĘ/Į±żŁ╣■ż▀Ī╦┬čĄū└Łż¼żóżĻĪóRRAMżŽź▐ź╣ź»┐¶ż╬╗\▓├ż¼2ĮŚż└ż▒ż╚żżż”ź│ź╣ź╚═ū░°żŌżóżļĪŻ

▓├ż©żŲĪ󿥿▐żČż▐ż╩ĄĪē”ż╬ź┴ź├źūż“ĮĖ└čż╣żļż╚żżż”┼└żŪĪó2.5Dżõ3Dż╬ĮĖ└čČ\ĮčżŌżóżļĪŻźšźĪź¾źóź”ź╚ż╬ź”ź¦Ī╝źŽźņź┘źļźčź├ź▒Ī╝źĖInFOČ\ĮčżõPoPĪ╩Package on packageĪ╦ĪóCoWoSĪ╩Chip on Wafer on SubstrateĪ╦ż╩ż╔ż╬Č\Įčż“┬Ęż©Ī󿥿ķż╦Chip on ChipĪ╩SoIC: System on Integrated ChipsĪ╦żõWoWĪ╩Wafer on WaferĪ╦ż╩ż╔ż╬3DČ\ĮčżŌżóżļĪŻWoWżŽN16źūźĒź╗ź╣żŪ╝┬Š┌żĄżņżŲż¬żĻĪóSoICČ\ĮčżŌN7źūźĒź╗ź╣żŪ└«Ė∙żĘżŲżżżļż╚żżż”ĪŻ2.5D/3D╝┬äóČ\ĮčżŪżŽĪ󱜎čż╬ASEż╚╚µż┘╚∙║┘▓ĮČ\ĮčżŪµ£ż»░Ńż”ż┐żßĪóĒö╣ńżĘż╩żżĪóż╚ZhangĢ■żŽĖņż├żŲżżżļĪŻ

╗▓╣═½@╬┴

1. ─ŠŖZż╬źšźĪź”ź¾ź╔źĻźķź¾źŁź¾ź░Īó2ĘÕź▐źżź╩ź╣└«─╣┤ļČ╚ż¼¶öĮą (2019/06/26)

2. źšźĪź”ź¾ź╔źĻ2╝ęż¼└«─╣└’ŠSż“ĖņżļĪ┴Samsungįć (2018/09/14)