AlteraĪó14nm FinFETźūźĒź╗ź╣║╬├ōż╬ĮķSoC×æēäStratix 10ż“╚»╔Į

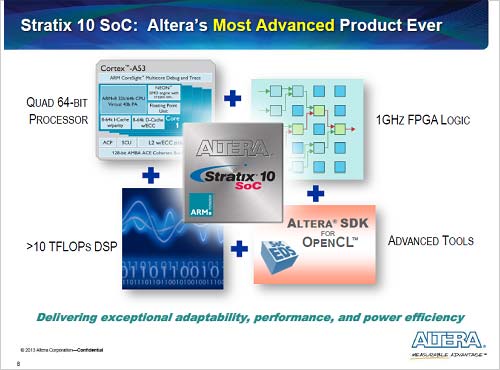

Alteraż¼Intelż╬14nm FinFETźūźĒź╗ź╣żŪÖ┌ŠÅż╣żļ┐ʿʿżSoCź┴ź├źūĪóStratix 10ż╦ż─żżżŲĪóżĮż╬Č\ĮčŲŌ═Ųż“żĶż”żõż»╚»╔ĮżĘż┐ĪŻż│ż╬SoCżŽĪóCPUż╦ARMż╬64źėź├ź╚źūźĒź╗ź├źĄCortex-A53ż“ĮĖ└čĪóŲ╚śOĄĪē”ż“Ęeż┐ż╗żļż┐żßż╦╝■╩šövŽ®ż╦FPGAż“├ōżżżŲżżżļĪŻ64źėź├ź╚×æēäż¼└@├ōż╬┴╚ż▀╣■ż▀źĘź╣źŲźÓż╦┼ļ║▄żĄżņżļ╗■┬Õż╦Ų═Ų■ż╣żļĪŻ

┐▐1ĪĪ14nm FinFETźūźĒź╗ź╣żŪÖ┌ŠÅż╣żļStratix 10 SoC×æēäĪĪĮąųZĪ¦Altera

FPGAż¼żóż▐żĻż╦żŌ╩Ż╗©ż╦ż╩żļż┐żßĪóµ£żŲźŽĪ╝ź╔ź’źżźõĪ╝ź╔źĒźĖź├ź»żŪövŽ®ż“┴╚żÓż╬żŪżŽż╩ż»ĪóCPUż“║«║▀żĄż╗Īó┤╦▄┼¬ż╩öU(ku©░)Ėµż╦żŽCPUĪó║╣╩╠▓ĮövŽ®ż╦żŽFPGAĪóż╚żżż”źóĪ╝źŁźŲź»ź┴źŃżžż╚╩čż’ż├żŲżŁżŲżżżļĪŻFPGAż╬╝Õ┼└żŽĪóźĮźšź╚ź”ź©źóż¼żĮż╬ż▐ż▐ź½ź╣ź┐źÓövŽ®żŪżóżļż½żķĪóźĮźšź╚½@ŠÅż“╗─ż╗ż╩żżż│ż╚ĪŻ╬«├ōżŌżŪżŁż╩żżĪŻCPUöĄ(sh©┤)╝░ż└ż╚ĪóövŽ®żŪżŽż╩ż»ĄĪē”ż“╝┬ĖĮż╣żļż┐żßż╬ź│Ī╝ź╔żŪżóżļż½żķĪóź│Ī╝ź╔ż“╬«├ōżŪżŁżļĘ┴ż╦─ŠżĘżõż╣żżĪŻ

ż│ż╬║Ū┐ĘSoCĪóStratix 10żŽĪ󟻟’ź├ź╔ź│źóCortex-A53ż“ĮĖ└čżĘż┐ż└ż▒żŪżŽż╩ż»Īó╔ŌŲ░Š«┐¶┼└▒ķōQ▓─ē”ż╩10Tera FLOPSż╬DSPĪó1GHzżŪŲ░║Ņż╣żļFPGAżŌĮĖ└čżĘżŲżżżļ(┐▐1)ĪŻCPUż╚DSPż╚żżż”źžźŲźĒż╩źūźĒź╗ź├źĄż“OpenCLżŪźūźĒź░źķź▀ź¾ź░żŪżŁżļ│½╚»ź─Ī╝źļSoC EDSżŌ─¾ČĪż╣żļĪŻ

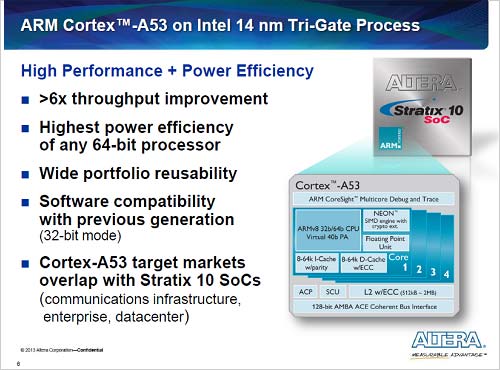

Cortex-A53żŽĪ󟻟’ź├ź╔ź│źóż▐żŪźĄź▌Ī╝ź╚żŪżŁżļ64źėź├ź╚źūźĒź╗ź├źĄź│źóżŪ(┐▐2)Īó1GHzżŪŲ░ż»Cortex-A9ż╚╚µż┘└Łē”żŽ6Ū▄ż└ż╚żżż”ĪŻ▓├ż©żŲ32źėź├ź╚╠┐╬ßżŌ×óż©ĪóźĮźšź╚ź”ź©źóż╬▓╝░╠Ė▀┤╣└Łż“Ęeż┴Īó▓Š„[▓Į╣Į└«żŌ▓─ē”ż└ż╚żĘżŲżżżļĪŻ

┐▐2ĪĪARM Cortex-A53 CPUĪĪĮąųZĪ¦Altera

AlterażŽĖ▄Ąęż╬═ūĄßż╚ź▐ź├ź┴ż╣żļSoCĖ■ż▒ż╬CPUż╚żĘżŲCortex-A53ż“┬ō(li©ón)ż¾ż└ĪŻżĄżķż╦╣Ō└Łē”ż╩ARMż╬Cortex-A57ż“║╬├ōżĘż╩ż½ż├ż┐═²Įy(t©»ng)ż“ĪóAlteraż╬SoC×æēäź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷źĘź╦źóźŪźŻźņź»ź┐żŪżóżļChris BaloughĢ■(hu©¼)(┐▐3)żŽ╝Īż╬żĶż”ż╦Įęż┘ż┐ĪŻĪųź│źóż“źĘźĻź│ź¾ż╦ĮĖ└čżĘż┐Šņ╣ńż╬ĀC└čż¼A57żŽA53ż╬3Ū▄żŌżóżĻĪóŠ├õJ┼┼╬üżŌĮj(lu©░)żŁżżĪŻżĄżķż╦źĒźżźõźļźŲźŻ▓┴│╩żŌ╣ŌżżĪūĪóż╩ż╔ż“Ą¾ż▓żŲżżżļĪŻźžźŲźĒż╩źūźĒź╗ź├źĄż“ĮĖ└čżĘż┐SoCż╬źūźĒź░źķź▀ź¾ź░ż“═Ų░ūż╦ż╣żļż┐żßż╬ź│ź¾źĮĪ╝źĘźóźÓżŪżóżļHSAĪ╩Heterogeneous System ArchitectureĪ╦Foundation(╗▓╣═½@╬┴1)ż╦żŽAlterażŽ▓├ż’ż├żŲżżż╩żżĪŻżĮż╬═²Įy(t©»ng)ż“Ų▒Ģ■(hu©¼)żŽĪóĪųHSAż╬×┤ō■(j©┤)ż╚ż╣żļSoCżŽźŽźżź©ź¾ź╔ż╬ź│ź¾źįźÕĪ╝źŲźŻź¾ź░źčź’Ī╝ż“║ŪĮj(lu©░)Ė┬ż╦╚»Ä¦ż╣żļ├ō²ŗż“┴└ż├ż┐żŌż╬żŪżóżĻĪóAlteraż╬SoCżŽżĮżņż“┴└ż├ż┐żŌż╬żŪżŽż╩żżĪŻż└ż½żķHSAż╦żŽ╗▓▓├żĘżŲżżż╩żżĪū

┐▐3ĪĪAltera SoC Product MarketingĪóSenior Directorż╬Chris BaloughĢ■(hu©¼)

ż│ż╬SoCż╬├ō²ŗżŽĪóźŪĪ╝ź┐ź╗ź¾ź┐Ī╝żõ─╠┐«źżź¾źšźķĪ╩┤├ŽČ╔Ī╦ĪóźņĪ╝ź└Ī╝źĘź╣źŲźÓż╩ż╔ż“„[─ĻżĘżŲżżżļż¼Īóż│ż│żŪż╬źŪĪ╝ź┐ź╗ź¾ź┐Ī╝żŽ╝ŖōQē”╬üż“╝{Ąßż╣żļżŌż╬żŪżŽż╩ż»ĪóĖ┬żķżņż┐ĀC└čż╬źėźļŲŌż╦└▀ÅøżĄżņĪó24╗■┤ų╔nŲ»żĘ¶öż▒Īóȧ╬õżŪŲ░║Ņż╣żļźĘź╣źŲźÓż“„[─ĻżĘżŲżżżļĪŻ

żŌż╚żŌż╚AlterażŽĪóźūźĒź░źķź▐źųźļźĒźĖź├ź»ż“├µ┐┤ż╚żĘż┐ICż“░Ęż├żŲżŁżŲĪó╝Īż╦źßźŌźĻż“ĮĖ└čĪóź╚źķź¾źĘĪ╝źąövŽ®ż╩ż╔żŌĮĖ└čżĘżŲżŁżŲĪó║ŪŖZżĶż”żõż»CPUżŌ┼ļ║▄ż╣żļżĶż”ż╦ż╩ż├ż┐┤ļČ╚ż└ĪŻIntelżõAMDż╩ż╔żŽCPUż╬└Łē”ż“╝{ĄßżĘżŲżŁż┐źūźĒź╗ź├źĄźßĪ╝ź½Ī╝żŪżóżĻĪó╚ÓżķżŽCPUż“├µ┐┤ż╦źĒźĖź├ź»żõGPUż╩ż╔ż╬źūźĒź╗ź├źĄż“ĮĖ└čżĘżŲżŁż┐ĪŻż│ż│ż╦░Ńżżż¼żóżļĪŻż└ż½żķAlterażŽHSAżž▓├Ų■ż“ż╗ż║ĪóźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╚żĘżŲżŌ╝ŖōQĄĪē”╬üż“─_£åż╣żļż╚ż│żĒż“┴└ż├żŲżżżļż’ż▒żŪżŽż╩żżĪŻż│ż╬Stratix 10żŽ╝ŖōQē”╬üżŪ▒M╔ķż╣żļźŽźżź©ź¾ź╔×æēäżŪżŽż╩ż»Īó└@├ō┼¬ż╩źŽźżź©ź¾ź╔ż“┴└ż├ż┐×æēäż╚Ė└ż©żļĪŻ

14nm FinFETźūźĒź╗ź╣ż“╗╚ż”źšźĪź”ź¾ź╔źĻż╚żĘżŲIntelż“┬ō(li©ón)ż¾ż└═²Įy(t©»ng)żŽż╣żŪż╦╩¾╠O(p©¬ng)żĘż┐Ī╩╗▓╣═½@╬┴2) ż¼Īóż│ż╬└ĶTSMCżŽż╔ż”ż╩żļż╬ż½ĪŻżĮżņż╦ż─żżżŲżŌ╩╣żżż┐ĪŻĪųż│żņż▐żŪ20nmż▐żŪżŽTSMCż“╗╚ż├żŲżŁż┐ĪŻĮø(j©®ng)═Ķż╬ź▌Ī╝ź╚źšź®źĻź¬ż╦ż─żżżŲżŽTSMCż╚żĶż»ÅBżĘ╣ńż├żŲżżżļĪŻż│ż╬└Ķż╦ż─żżżŲżŌTSMCż“╗╚ż”ż╚żżż”┬ō(li©ón)┘I(m©Żi)╗Ķż╦╩čż’żĻżŽż╩żżĪŻż┐ż└Īó14nm FinFETż╬║ŪĮķż╬×æēäż“Ö┌ŠÅ░č▓mż╣żļŠņ╣ńĪóIntelż╬źūźĒź╗ź╣źņź┘źļż¼║ŪżŌ╣Ōż»ĪóĖĮ╝┬┼¬ż╩14nm FinFETźūźĒź╗ź╣żŪÖ┌ŠÅżŪżŁżļźšźĪź”ź¾ź╔źĻżŽIntelżĘż½żżż╩żżĪŻ║ŪĮķż╦Įą▓┘żĘż┐22nmż╬ŗī1└ż┬Õż╬FinFET┼ļ║▄×æē俎ż╣żŪż╦1▓»Ė─ż╬Įą▓┘╝┬└ėż¼żóżļĪŻ14nmżŽŗī2└ż┬Õż╬FinFETźūźĒź╗ź╣ż╚ż╩żļż¼ĪóżõżŽżĻ┴Ļ×┤┼¬ż╦Intelż¼Ń~ŠW(w©Żng)ż└żĒż”ĪūĪŻ

Ę└╠¾ż╦ż─żżżŲĪóIntelż╬14nm FinFETźūźĒź╗ź╣żŽŲ╚žéĘ└╠¾(ź©ź»ź╣ź»źļĪ╝źĘźų)ż└ż╚żżż”ĪŻż┐ż└żĘĪó┬Šż╬Ēö╣ńż╣żļFPGAźßĪ╝ź½Ī╝Ī╩XilinxżõLatticeż╩ż╔Ī╦ż╦×┤żĘżŲż╬ź©ź»ź╣ź»źļĪ╝źĘźųżŪżóżĻĪó└Ķ╣įżĘżŲżżżļTabulaż╩ż╔ż╬ź┘ź¾ź┴źŃĪ╝ż╦żŽ┼¼├ōżĄżņż╩żżż╚żĘżŲżżżļĪŻ

Stratix 10×æēäż╬źŲĪ╝źūźóź”ź╚żŽ2014ŃQŗī1╗═╚Š┤³ż“═Į─ĻżĘżŲżżżļĪŻźĄź¾źūźļĮą▓┘╗■┤³żŽ£½│╬ż╦żĘżŲżżż╩żżż¼Īó─╠Š’żŽ12~16ĮĄĖÕż╦ż╩żļż╚ż╣żļĪŻ

╗▓╣═½@╬┴

1. ╩Ż╗©ż╩SoCż“į~├▒ż╦└▀╝Ŗż╣żļż┐żßż╬ź─Ī╝źļż“║YØŹ▓ĮżĘżĶż”Ī▌HSAż¼Ō}żėż½ż▒ (2013/09/13)

2. AlteraĪó14nmż╬IntelźšźĪź”ź¾ź╔źĻĪó55nmźšźķź├źĘźÕĪóźĒĪ╝ź╔ź▐ź├źūż“Ėņżļ (2013/05/02)