2024年5月17日

Ī├Č\Įč╩¼└ŽĪ╩╚ŠŲ│öü×æēäĪ╦

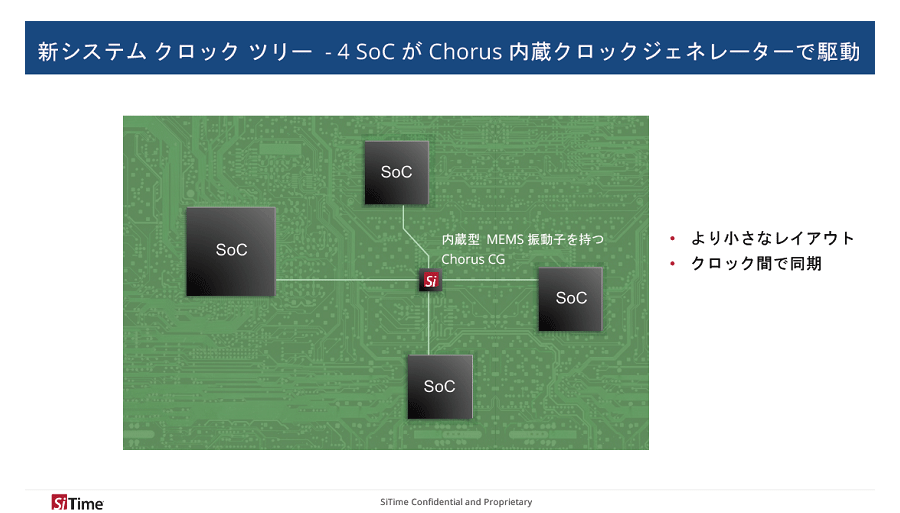

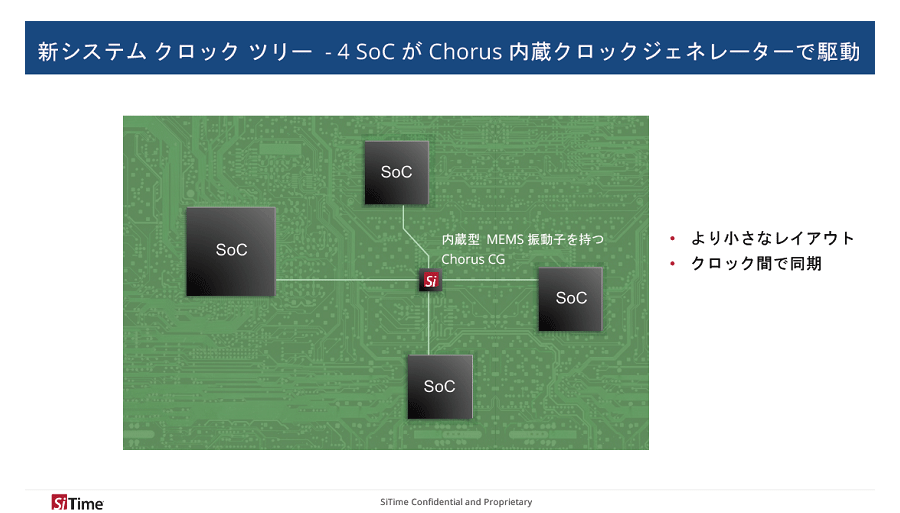

MEMSż“ŠW├ōż╣żļ┐ČŲ░╗ęż╚╚»┐ČövŽ®Ī󟻟Ēź├ź»╚»Ö┌▀_ż“1źčź├ź▒Ī╝źĖż╦╝┬äóżĘż┐ź»źĒź├ź»ICżŽĪóŠ«Ę┐Īó╣Ō└Łē”Īó─Ńź╬źżź║ż└ż▒żŪżŽż╩ż»Ī󟻟Ēź├ź»╝■żĻż╬źūźĻź¾ź╚┤ł└▀╝ŖżŌį~░ūż╦żĘżŲż»żņżļĪŻMEMSź┘Ī╝ź╣ż╬ź»źĒź├ź»ICż“Š}²Xż▒żŲżŁż┐SiTimeż¼4ż─ż╬SoCż“Ų▒╗■ż╦ź»źĒź├ź»żŪżŁżļ4Įą╬üż╬ź»źĒź├ź»ICĪųChorusĪūż“×æēä▓ĮżĘż┐ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年5月17日

Ī├Č\Įč╩¼└ŽĪ╩╚ŠŲ│öü×æēäĪ╦

źķźįź└ź╣ż¼RISC-Vż╬ź╣ź┐Ī╝ź╚źóź├źūEsperanto Technologiesż╚Ė“ż’żĘż┐─¾Ę╚żŽĪó╝┬żŽż│ż│żŪĮķżßżŲTSMCż╚ż╬░Ńżżż¼£½│╬ż╦ĮążŲżżż┐ĪŻEsperantoż╬▓±Ė½żŪżŽÜW║═CPUźŪźČźżź╩Ī╝ż╚żŌĖ└ż’żņżļDave Ditzel CTOĪ╩┐▐1Ī╦żŌŲ▒└╩żĘżŲżżż┐ż╬ż└ĪŻ╚ÓżŽż½ż─żŲźĮźšź╚ź”ź©źóż╦żĶżļ╣®╔ūżŪX86Ė▀┤╣źūźĒź╗ź├źĄż“└▀╝ŖżĘĪó║ŻżŽRISC-Vż╬└▀╝Ŗż“╬©żżżļĪŻ╚Óż¼TSMCż╚ż╬░Ńżżż“£½│╬ż╦żĘż┐ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年4月15日

Ī├ĮĄ┤ųź╦źÕĪ╝ź╣╩¼└Ž

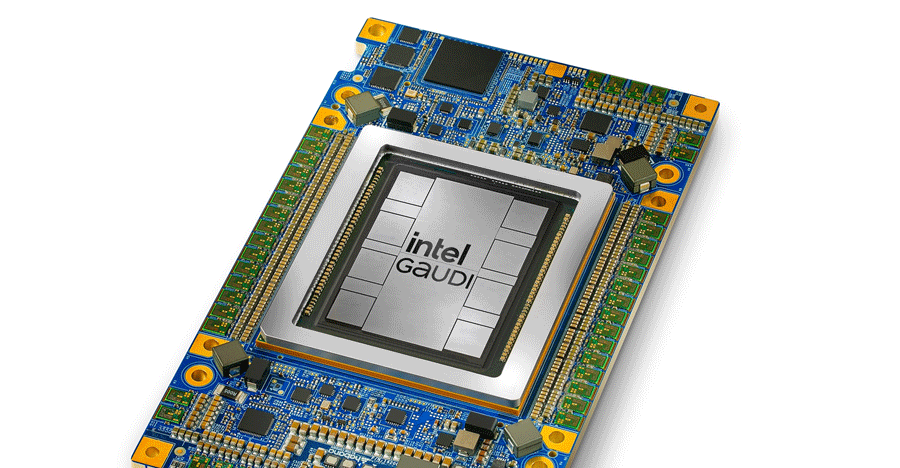

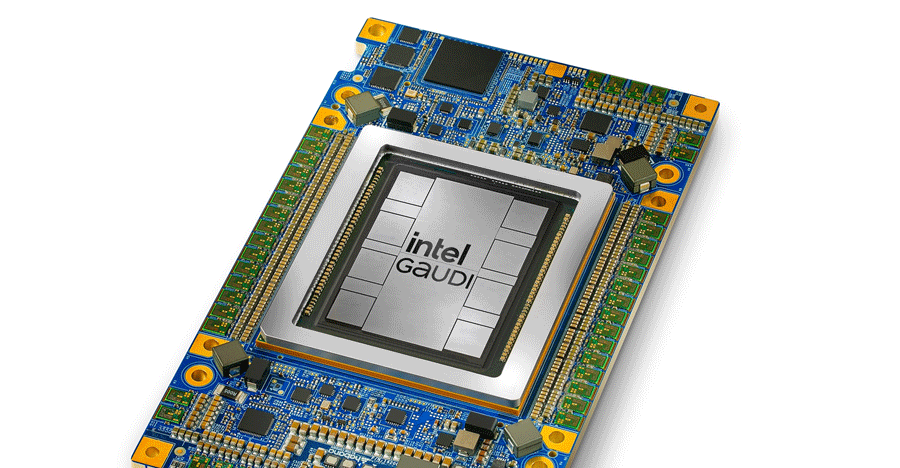

AIČ\Į迎ź»źķź”ź╔żŌź©ź├źĖżŌČ”ż╦īÖ╚»ż└ż¼Īó└ĶĮĄżŽź»źķź”ź╔ż“Ū░Ų¼ż╦Åøż»źŪĪ╝ź┐ź╗ź¾ź┐Ī╝├ō²ŗżŪż╬AIź┴ź├źūż╬┐Ę×æēäż¼Intelż╚MetaĪ╩ĄņFacebookĪ╦ż½żķ╚»╔Įż¼żóżĻĪóArmżŌ┐ĘAI IPź│źóż“ĪóGoogleżŽź╣ź╚źņĪ╝źĖöUĖµż╬CPUż“╚»╔ĮżĘż┐ĪŻAIź┴ź├źūż╬ź╣ź┐Ī╝ź╚źóź├źūTenstorrentż╚─¾Ę╚żĘż┐źķźįź└ź╣ż¼źĘźĻź│ź¾źąźņĪ╝ż╦▒─Č╚Ą“┼└ż“Åøż»ĪŻźļź═źĄź╣żŽ╣├ĮB╣®Šņż“╔nŲ»│½╗ŽżĘż┐ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年4月 9日

Ī├Č\Įč╩¼└ŽĪ╩╚ŠŲ│öü×æēäĪ╦

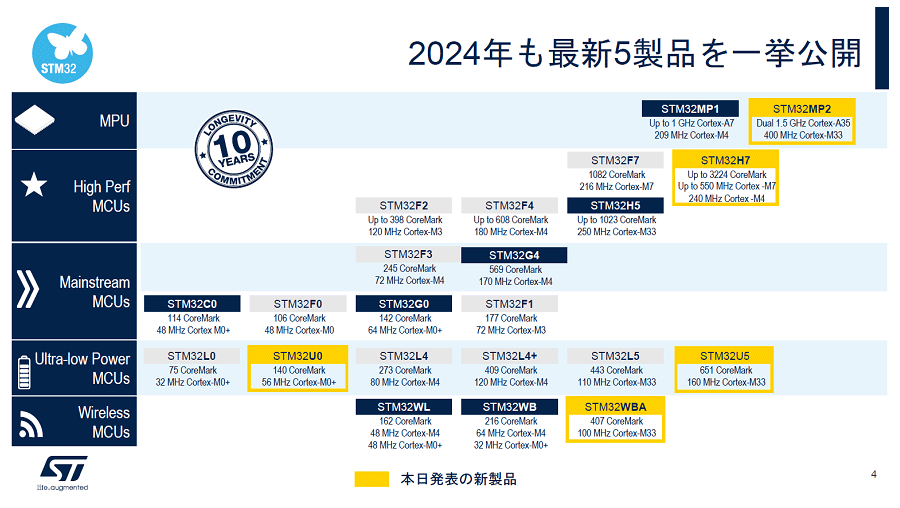

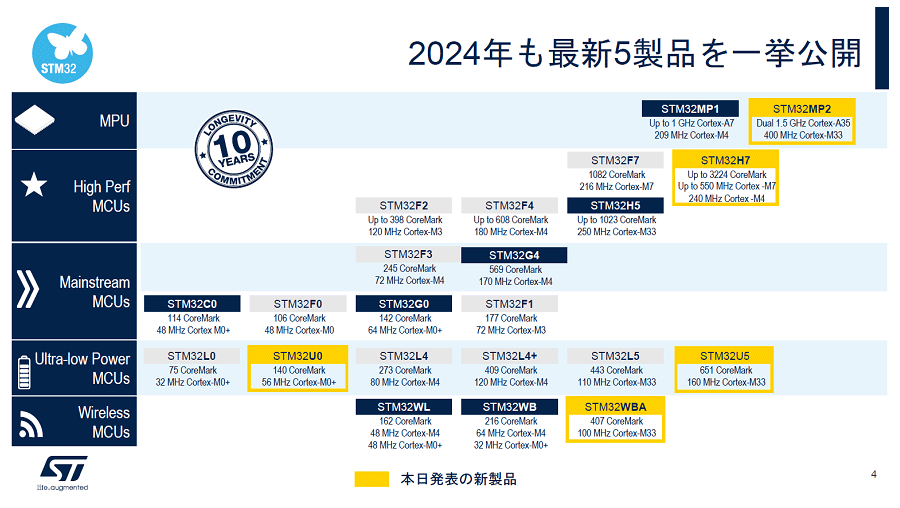

STMicroelectronicsż¼ź▐źżź│ź¾ż╬×æēäź▌Ī╝ź╚źšź®źĻź¬ż“│╚ĮjżĘżŲżŁż┐ĪŻŠ«żĄż╩ģ╬═█┼┼├ėżŪŲ░║Ņż╣żļź©ź═źļź«Ī╝źŽĪ╝ź┘ź╣źŲźŻź¾ź░├ō²ŗż╬ź▐źżź│ź¾ż½żķĪ󿥿ķż╦żŽźŽźżź©ź¾ź╔ź▐źżź│ź¾ż╚żĘżŲź│ź╣ź╚Ė·╬©ż╬╣ŌżżCortex-A35ż╚Cortex-M33ż“ĮĖ└čż╣żļSoC+MCUż▐żŪSTM32źĘźĻĪ╝ź║ż╚żĘżŲ│╚ĮjżĘż┐ĪŻ║ŻĖÕ18nmź╬Ī╝ź╔ż╬FD-SOIźūźĒź╗ź╣PCMźßźŌźĻĮĖ└čź▐źżź│ź¾żŌ24ŃQĖÕ╚ŠźĄź¾źūźļĮą▓┘ż╣żļ═Į─Ļż└ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年3月29日

Ī├ŠÅČ╚╩¼└Ž

IntelżŽĪó2ĘŅż╦ĪųIntel Foundry Direct Connect 2024Īūż“│½╠¢ĪóżĮż╬▐kŗĪ╩╗▓╣═½@╬┴1Ī╦ż“ż╣żŪż╦╩¾╣żĘż┐ż¼ĪóżĮż╬Š▄║┘ż¼£½żķż½ż╦ż╩ż├ż┐ĪŻIntelżŽśOżķż“ĪųAI╗■┬Õż╬źĘź╣źŲźÓźšźĪź”ź¾ź╔źĻĪūż╚Ō}ż¾żŪżżżļż¼ĪóżĮż╬├µ┐╚ż“£½│╬ż╦─Ļ▒IżĘż┐ĪŻĖĮ║▀żŽ└ż─cźķź¾ź»żŪ10░╠¤²ŖZż╦żżżļż¼Īó2030ŃQż▐żŪż╦TSMCż╦╝Īż░ŗī2░╠ż╦ż╩żļĪóż╚£½Ė└żĘżŲżżżļĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

![2nmż╬ź▐ź╣ź»×æ║Ņ┤³┤ųż“│╩├╩ż╚ø]Į╠ż╣żļNvidiaż╬cuLithoż╚Synopsysż╬OPC 2nmż╬ź▐ź╣ź»×æ║Ņ┤³┤ųż“│╩├╩ż╚ø]Į╠ż╣żļNvidiaż╬cuLithoż╚Synopsysż╬OPC](/assets_c/900px/240328-culitho.png)

2024年3月28日

Ī├Č\Įč╩¼└ŽĪ╩źūźĒź╗ź╣Ī╦

2nmźūźĒź╗ź╣żŪżŽĪóEUVż╚żżż©ż╔żŌOPCĪ╩Ė„│ž┼¬ŖZ└▄Ė·▓╠T┘ćĪ╦ż¼ØŁ═ūż╦ż╩ż├żŲż»żļĪŻEUVż╬13.5nmż╚żżż”āS─╣żŪżŽźčź┐Ī╝ź¾ż“żĮż╬ż▐ż▐▓├╣®żŪżŁż╩ż»ż╩ż├żŲżŁż┐ż½żķż└ĪŻ2nmźūźĒź╗ź╣ż└ż╚╩Ż╗©ż╣ż«żŲ╗Ņ╣įēžĖĒ┼¬ż╩źóźūźĒĪ╝ź┴żŽżŌżŽżõ╗╚ż©ż╩żżĪŻ╝ŖōQĄĪŠW├ōż╬źĻźĮź░źķźšźŻż╬Įą╚ųż╚ż╩żļĪŻNvidiaż╚TSMCĪóSynopsysĪóASMLżŽĪó║“ŃQź©ź│źĘź╣źŲźÓż“╣Į├█żĘż┐ż¼Ī╩╗▓╣═½@╬┴1Ī╦ĪóTSMCż╬╬╠ŠÅźķźżź¾ż╦╝ŖōQĄĪźĻźĮż“Ų│Ų■żĘżŲżżżļż│ż╚ż¼£½żķż½ż╦ż╩ż├ż┐ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年3月22日

Ī├Č\Įč╩¼└ŽĪ╩╚ŠŲ│öü×æēäĪ╦

╚ŠŲ│öüĮķż╬╗■▓┴┴Ē±Y1├¹ź╔źļ┤ļČ╚ż╚ż╩ż├ż┐Nvidiaż╬▐kĮjźżź┘ź¾ź╚żŪżóżļGTC 2024ż¼║ŻĮĄĮķżßż╦ä▌ź½źĻźšź®źļź╦źó䔟Ąź¾ź╬ź╝żŪ│½╠¢żĄżņĪó1├¹źčźķźßĪ╝ź┐ż“ĮĶ═²ż╣żļż┐żßż╬┐ʿʿżAIź┴ź├źūĪųGB200Īūż“£½żķż½ż╦żĘż┐ĪŻż│ż╬×æē俎Īó┐ĘGPUĪųBlackwellĪūż“2Ė─ż╚CPUĪųGraceĪū1Ė─ż“ĮĖ└čżĘż┐SiPĪ╩System in PackageĪ╦ĪŻBlackwellżŌĪó2ź┴ź├źū╣Į└«ż╚ż╩ż├żŲż¬żĻĪóGPU1Ė─żŪżŌĄĮjż╩ź┴ź├źūż╚ż╩ż├żŲżżżļĪŻż╩ż╝ĄĮjż╩ź┴ź├źūż¼ØŁ═ūż½ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年3月19日

Ī├Č\Įč╩¼└ŽĪ╩╚ŠŲ│öü×æēäĪ╦

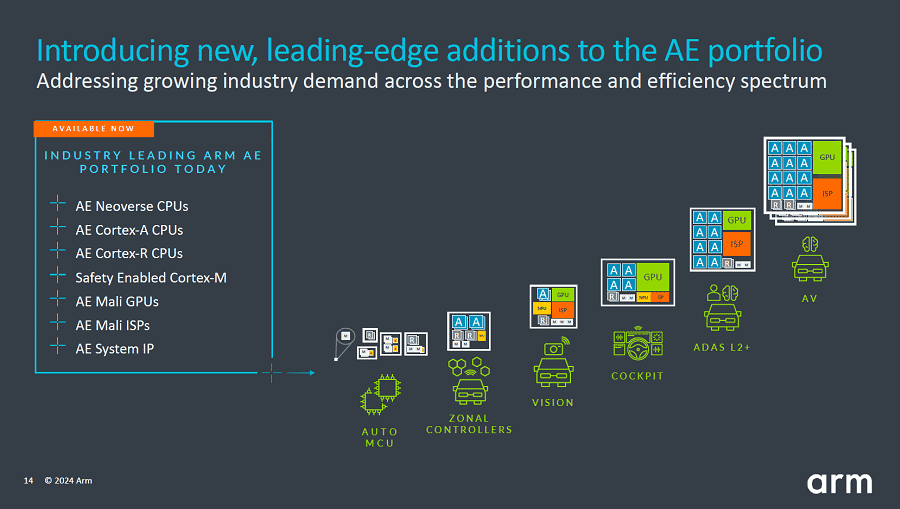

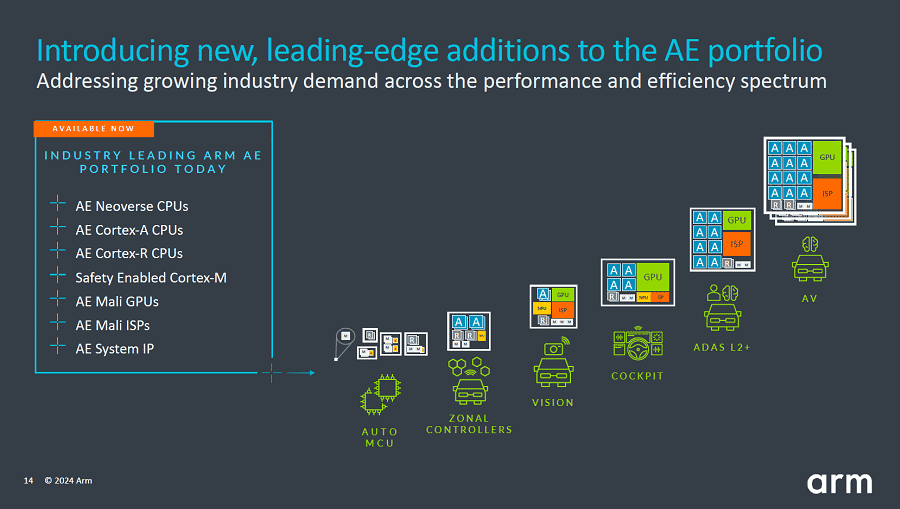

ArmżŽ3ĮĄ┤ųż█ż╔Øiż╦źŪĪ╝ź┐ź╗ź¾ź┐Ī╝├ōż╬źŽźżź©ź¾ź╔ż╬CPUź│źóĪųNeoverse N3/V3ĪūźĘźĻĪ╝ź║ż╬CPUż“źĻźĻĪ╝ź╣żĘż┐ż¼Īóż╣żŪż╦ź»źļź▐ź░źņĪ╝ź╔ż╬Neoverse V3AE IP×æēäż“─¾ČĪżĘż┐ż│ż╚ż“£½żķż½ż╦żĘż┐ĪŻż│ż╬IPżŽĪóASIL-B/DżõISO26262ż╩ż╔┘Z║▄╗┼══ż“╦■ż┐żĘĪóż│ż╬źĘźĻĪ╝ź║ż└ż▒żŪżŽż╩ż»ĪóAutomotive EnhancedźĘźĻĪ╝ź║ż╚żĘżŲĪóCortex-A/R/Mż╩ż╔ż╬źĘźĻĪ╝ź║ż╦żŌŲ│Ų■ż╣żļĪ╩┐▐1Ī╦ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年3月15日

Ī├Č\Įč╩¼└ŽĪ╩╚ŠŲ│öü▒■├ōĪ╦

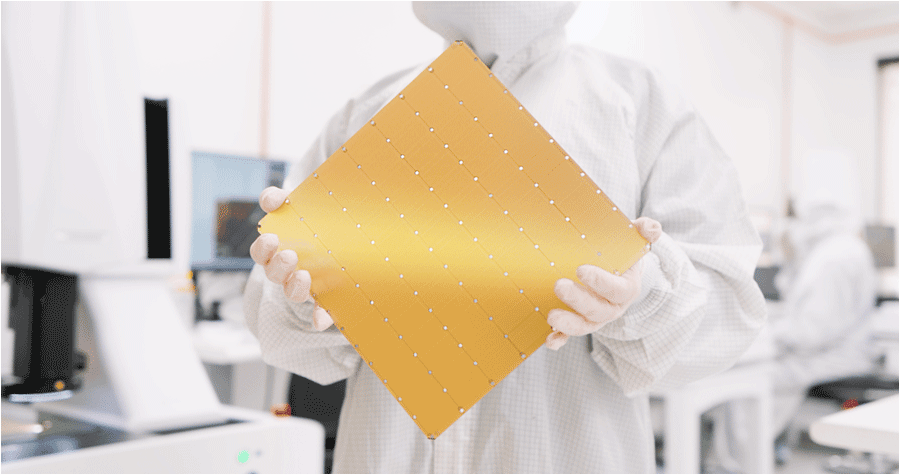

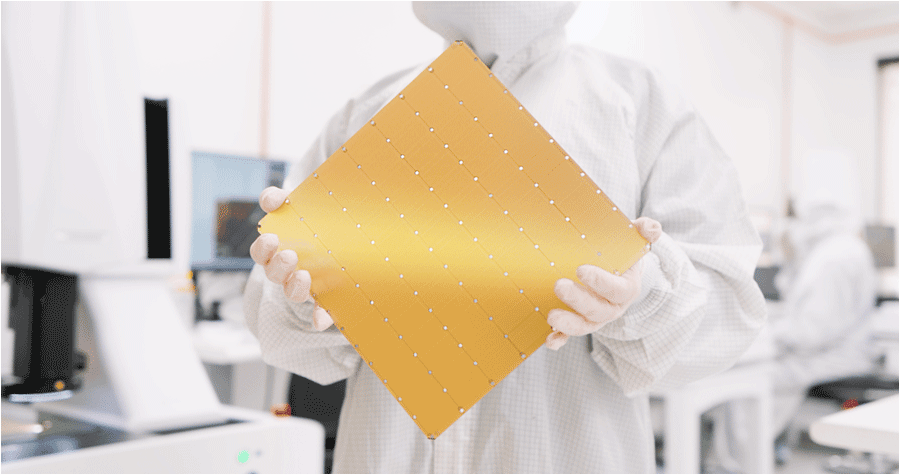

Cerebras Systems╝꿎Īó4├¹ź╚źķź¾źĖź╣ź┐ż“ĮĖ└čżĘż┐ź”ź¦Ī╝źŽź╣ź▒Ī╝źļż╬AIźóź»ź╗źķźņĪ╝ź┐ź┴ź├źūĪųWSE-3Īūż“│½╚»żĘż┐ĪŻ300mmź”ź¦Ī╝źŽż½żķ21cm│čż╦└┌żĻŲDż├ż┐╚ŠŲ│öüżŪĪóØiövż╬WSE-2Ī╩╗▓╣═½@╬┴1Ī╦żŪż╬7nmż½żķ5nmźūźĒź╗ź╣ż“ŠW├ōżĘżŲĮĖ└č┼┘ż“æųż▓ż┐ĪŻż│ż╬ź”ź¦Ī╝źŽź╣ź▒Ī╝źļICż“┴╚ż▀╣■ż¾ż└AIź│ź¾źįźÕĪ╝ź┐ĪųCS-3Īūż“64±ś┴╚ż▀╣■żÓĪųCondor Galaxy 3Īūż“└’ŠS┼¬źčĪ╝ź╚ź╩Ī╝żŪżóżļG42ż╚Č”Ų▒żŪ│½╚»├µżŪżóżļĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年3月14日

Ī├Č\Įč╩¼└ŽĪ╩źŪźąźżź╣└▀╝Ŗ& FPDĪ╦

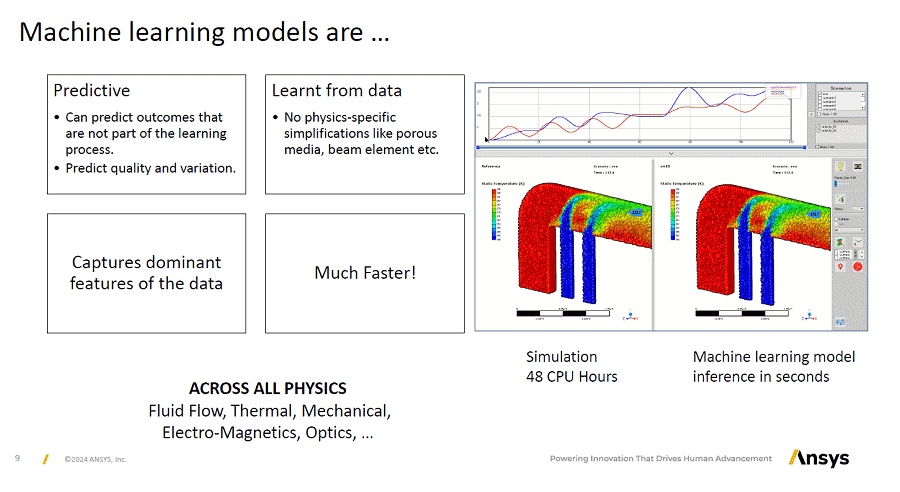

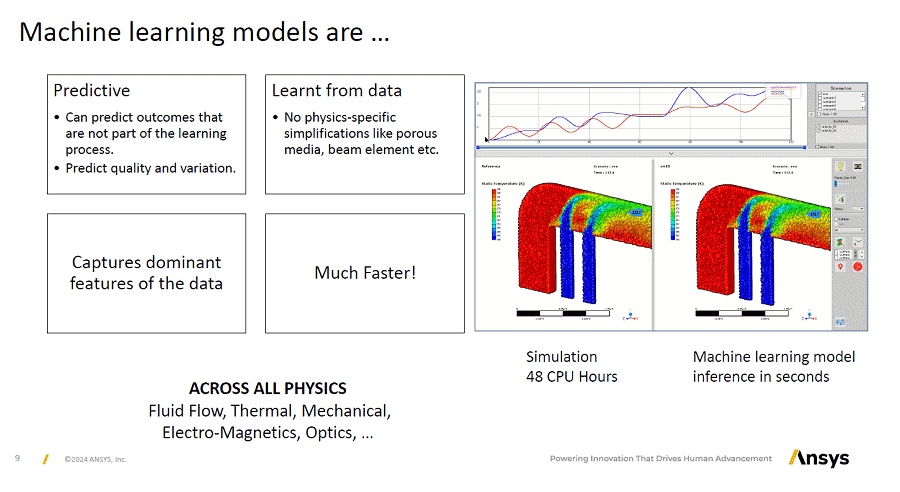

└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░żŪ─_═ūż╦ż╩żļĪó╬«öü▓“└Žżõ╣Įļ]▓“└Žż╩ż╔ż╬źĘź▀źÕźņĪ╝źĘźńź¾Č\Įčż╦AI/MLĪ╩ĄĪ│Ż│žØ{Ī╦ż“ŠW├ōż╣żļż╚ĪóĘÕ░Ńżżż╦±T▓╠ż¼Å]ż»įużķżņżļAIźĘź╣źŲźÓĪųSimAIĪūż“źĘź▀źÕźņĪ╝źĘźńź¾ź┘ź¾ź└Ī╝ż╬Ansysż¼│½╚»żĘż┐ĪŻAnsysżŽTSMCż╬ź©ź│źĘź╣źŲźÓż╦żŌEDA3╝ęż╚Č”ż╦╗▓▓├żĘżŲż¬żĻĪóż│żņż½żķż╬╚ŠŲ│öüźčź├ź▒Ī╝źĖż╦żŽ’Lż½ż╗ż╩ż»ż╩żĻżĮż”ż╩┘T║▀ż└ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

![2nmż╬ź▐ź╣ź»×æ║Ņ┤³┤ųż“│╩├╩ż╚ø]Į╠ż╣żļNvidiaż╬cuLithoż╚Synopsysż╬OPC 2nmż╬ź▐ź╣ź»×æ║Ņ┤³┤ųż“│╩├╩ż╚ø]Į╠ż╣żļNvidiaż╬cuLithoż╚Synopsysż╬OPC](/assets_c/900px/240328-culitho.png)